Hi Psyborg,

thank you for Your patience. I am very new to linux.. imagine about embedded ones.

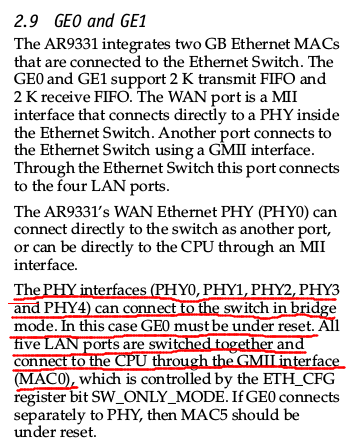

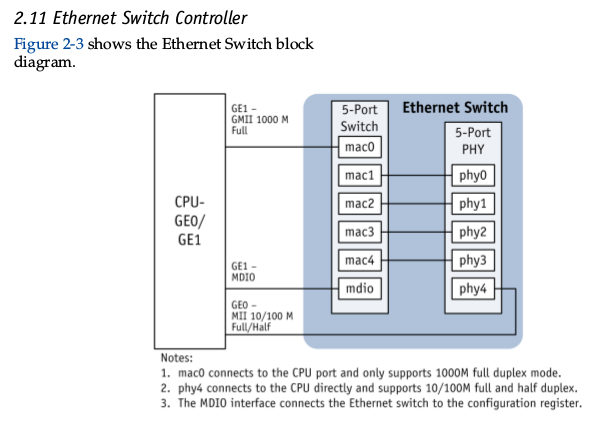

ar150 uses 9330(or 9331)soc carambola2 uses the same chipset, TP-LINK TL-WR940N v4 too.

So my idea was to figure out the difference between the 3 machines surfing the openwrt build directory.

I found differences in target/linux/ath79/base-files/etc/board.d/02_network

and in all files in target/linux/ar71xx/files/arch/mips/ath79/

like mach-gl-ar150.c, mach-wifi-pineapple-nano.c, mach-tl-wr940n-v4.c

in these last ones

like ar150 says ..

.......

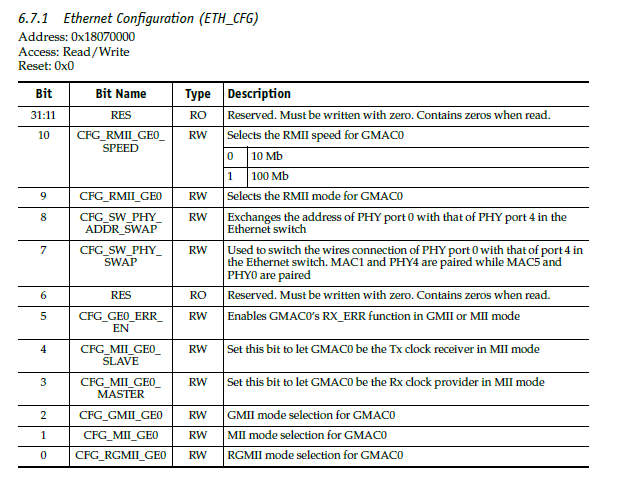

/* disable PHY_SWAP and PHY_ADDR_SWAP bits */

ath79_setup_ar933x_phy4_switch(false, false);

................

/* register eth0 as WAN, eth1 as LAN */

ath79_init_mac(ath79_eth0_data.mac_addr, art+GL_AR150_MAC0_OFFSET, 0);

ath79_init_mac(ath79_eth1_data.mac_addr, art+GL_AR150_MAC1_OFFSET, 0);

ath79_register_mdio(0, 0x0);

ath79_register_eth(0);

ath79_register_eth(1);

......................

wifi pineapple:

...........

ath79_setup_ar933x_phy4_switch(false, false);

ath79_register_mdio(0, 0x0);

ath79_init_mac(ath79_eth0_data.mac_addr,

art + WIFI_PINEAPPLE_NANO_MAC1_OFFSET, 0);

ath79_register_eth(0);

..............................

tl-wr940n-v4.c

....................

ath79_init_mac(ath79_eth0_data.mac_addr, mac, 1);

ath79_init_mac(ath79_eth1_data.mac_addr, mac, -1);

ath79_switch_data.phy4_mii_en = 1;

ath79_register_eth(0);

ath79_register_eth(1);

......................................

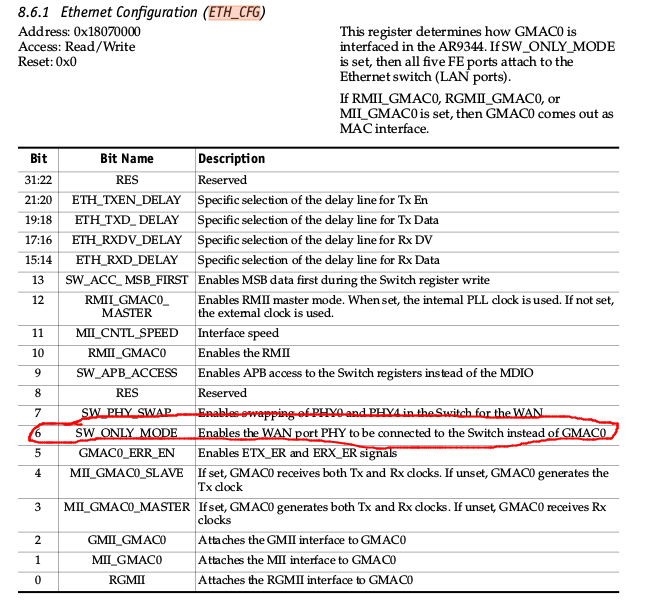

then with a different SOC (ar9344 with switch AR8327) wndr4300 :

..............................................

ath79_setup_ar934x_eth_cfg(AR934X_ETH_CFG_RGMII_GMAC0);

mdiobus_register_board_info(wndr4300_mdio0_info,

ARRAY_SIZE(wndr4300_mdio0_info));

ath79_register_mdio(0, 0x0);

/* GMAC0 is connected to an AR8327N switch */

ath79_eth0_data.phy_if_mode = PHY_INTERFACE_MODE_RGMII;

ath79_eth0_data.phy_mask = BIT(0);

ath79_eth0_data.mii_bus_dev = &ath79_mdio0_device.dev;

ath79_eth0_pll_data.pll_1000 = 0x06000000;

ath79_register_eth(0);

...........................................

inside target/linux/ar71xx/base-files/etc/board.d/02_network

#!/bin/sh

Copyright (C) 2011-2015 OpenWrt.org

. /lib/functions/system.sh

. /lib/functions/uci-defaults.sh

ar71xx_setup_interfaces()

{

local board="$1"

case "$board" in

..............

wifi-pineapple-nano|\

..........

gl-ar150|\

.....................

tl-wr940n-v4|\

........................

wndr4300)

ucidef_add_switch "switch0"

"0@eth0" "1:lan:4" "2:lan:3" "3:lan:2" "4:lan:1" "5:wan"

...................................

My questions are:

1--- target/linux/ar71xx/base-files/etc/board.d/02_network

defines the UCI configuration after the network devices are already loaded in the kernel ? yes or no ?

(is it the right wording or should I say something different) ?

2--- the only references to interfaces are the ath9_register_eth(0) in the mac-XXX files

are these files responsible for the loading or configuration of the network device driver definition in the kernel ?

(is it the right wording or should I say something different) ?

3-- how if is possible (I could borrow the 4300 set up and apply it to ar150 to have the 2 ethernet sockets

(the plug on my minirouter) be handled by the built in switch ??

Remember everything started from the ar9331 datasheet claiming about the built-in switch

4-- why in the

target/linux/ar71xx/files/arch/mips/ath79/Kconfig.openwrt:

.....

config ATH79_MACH_GL_AR150

bool "GL AR150 support"

select SOC_AR933X

select ATH79_DEV_ETH

select ATH79_DEV_GPIO_BUTTONS

select ATH79_DEV_LEDS_GPIO

select ATH79_DEV_M25P80

select ATH79_DEV_USB

select ATH79_DEV_WMAC

...................

there is nothing about a switch ? I mean I could be wrong but to me sounds like

select ATH79_DEV_ETH will load a driver for ethernet controller/devices/whathever ?(right ? wrong)?

why I dont have anything related to switch ??

5-- what is the 03_network-switchX-migration in target/linux/ar71xx/etc about ?

in some lines I can read:

............................

rb-2011uas-2hnd)

migrate_switch_name "eth0" "switch0"

migrate_switch_name "eth1" "switch1"

..............................

So eth0 could refer to both a switch or a normal single physical interface ??

How I can distinguish between them ?

Hope my question are clear to You, to me they are kind out of the logic I think I its behind openwrt

but I feel I am kind far from the right track at the moment.

THanks

P.