@ilyas rc1-mt7615e-1 to rc-mt7615e-2. I've tried to flash it through wifi from phone

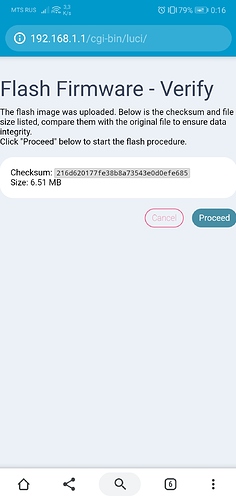

maybe it caused this problem) I've uploaded openwrt-ramips-mt7621-xiaomi_mir3p-squashfs-sysupgrade.bin on the first screen, that apppears on rc1-mt7615-1 when entering http://192.168.1.1 and that how I get down my r3p

maybe it caused this problem) I've uploaded openwrt-ramips-mt7621-xiaomi_mir3p-squashfs-sysupgrade.bin on the first screen, that apppears on rc1-mt7615-1 when entering http://192.168.1.1 and that how I get down my r3p

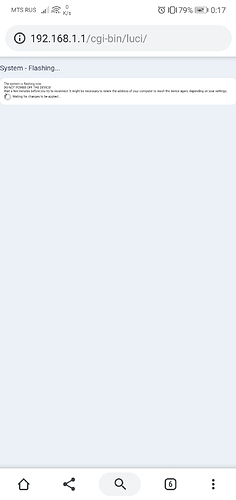

here is the last screenshots

here is the last screenshots

@pellmen as much as I'd like to believe that "it wasn't my fault", i'm pretty sure it is. did you notice that the boot message was kernel 4.14.93??!! it should have been 103... maybe it was just the factory.bin file that was botched... anyway, given that brokenness, i'm going to assume that it was a build problem on my part, and not investigate further (and the uart companies give me a kickback...)

i tested sysupgrading from rc-mt7615e-2 to itself and that worked fine... so sysupgrade is fine. transient failure.

this all gets me thinking... it would be really nice to have a feature that says "if we're bootlooping, go back to kernel0 so we can do usb recovery"....

I confirm. sysupgrade is fine

@ilyas here's the log:

=

===================================================================

MT7621 stage1 code May 28 2018 14:51:28 (ASIC)

CPU=50000000 HZ BUS=16666666 HZ

==================================================================

Change MPLL source from XTAL to CR...

do MEMPLL setting..

MEMPLL Config : 0x11100000

3PLL mode + External loopback

=== XTAL-40Mhz === DDR-1200Mhz ===

PLL3 FB_DL: 0xc, 1/0 = 669/355 31000000

PLL4 FB_DL: 0x11, 1/0 = 594/430 45000000

PLL2 FB_DL: 0x1d, 1/0 = 567/457 75000000

do DDR setting..[00320381]

Apply DDR3 Setting...(use customer AC)

0 8 16 24 32 40 48 56 64 72 80 88 96 104 112 120

--------------------------------------------------------------------------------

0000:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0001:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0002:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0003:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0004:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0005:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0006:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0007:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0008:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0009:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000A:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000B:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000C:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000D:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000E:| 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1

000F:| 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 0

0010:| 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0 0

0011:| 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0

0012:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0013:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0014:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0015:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0016:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0017:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0018:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0019:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001A:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001B:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001C:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001D:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001E:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001F:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

DRAMC_DQSCTL1[0e0]=13000000

DRAMC_DQSGCTL[124]=80000033

rank 0 coarse = 15

rank 0 fine = 80

B:| 0 0 0 0 0 0 0 0 0 0 1 1 1 0 0 0

opt_dle value:11

DRAMC_DDR2CTL[07c]=C287223D

DRAMC_PADCTL4[0e4]=000044B3

DRAMC_DQIDLY1[210]=07090709

DRAMC_DQIDLY2[214]=03070506

DRAMC_DQIDLY3[218]=08090807

DRAMC_DQIDLY4[21c]=08070907

DRAMC_R0DELDLY[018]=00001D1E

==================================================================

RX DQS perbit delay software calibration

==================================================================

1.0-15 bit dq delay value

==================================================================

bit| 0 1 2 3 4 5 6 7 8 9

--------------------------------------

0 | 7 3 5 6 5 3 5 3 5 5

10 | 7 7 7 8 7 8

--------------------------------------

==================================================================

2.dqs window

x=pass dqs delay value (min~max)center

y=0-7bit DQ of every group

input delay:DQS0 =30 DQS1 = 29

==================================================================

bit DQS0 bit DQS1

0 (0~56)28 8 (1~54)27

1 (1~52)26 9 (1~52)26

2 (1~51)26 10 (1~53)27

3 (1~57)29 11 (1~55)28

4 (1~57)29 12 (1~58)29

5 (1~55)28 13 (1~55)28

6 (1~55)28 14 (1~58)29

7 (1~60)30 15 (1~57)29

==================================================================

3.dq delay value last

==================================================================

bit| 0 1 2 3 4 5 6 7 8 9

--------------------------------------

0 | 9 7 9 7 6 5 7 3 7 8

10 | 9 8 7 9 7 8

==================================================================

==================================================================

TX perbyte calibration

==================================================================

DQS loop = 15, cmp_err_1 = ffff0000

dqs_perbyte_dly.last_dqsdly_pass[0]=15, finish count=1

dqs_perbyte_dly.last_dqsdly_pass[1]=15, finish count=2

DQ loop=15, cmp_err_1 = ffff01a2

DQ loop=14, cmp_err_1 = ffff0000

dqs_perbyte_dly.last_dqdly_pass[0]=14, finish count=1

dqs_perbyte_dly.last_dqdly_pass[1]=14, finish count=2

byte:0, (DQS,DQ)=(8,8)

byte:1, (DQS,DQ)=(8,8)

DRAMC_DQODLY1[200]=88888888

DRAMC_DQODLY2[204]=88888888

20,data:88

[EMI] DRAMC calibration passed

===================================================================

MT7621 stage1 code done

CPU=50000000 HZ BUS=16666666 HZ

===================================================================

U-Boot 1.1.3 (Sep 25 2018 - 12:04:25)

Board: Ralink APSoC DRAM: 256 MB

Power on memory test. Memory size= 256 MB...OK!

relocate_code Pointer at: 8ffac000

Config XHCI 40M PLL

Allocate 16 byte aligned buffer: 8ffe0010

Enable NFI Clock

# MTK NAND # : Use HW ECC

NAND ID [C8 DA 90 95 44]

Device found in MTK table, ID: c8da, EXT_ID: 909544

Support this Device in MTK table! c8da

select_chip

[NAND]select ecc bit:4, sparesize :64 spare_per_sector=16

Signature matched and data read!

load_fact_bbt success 2047

load fact bbt success

[mtk_nand] probe successfully!

mtd->writesize=2048 mtd->oobsize=64, mtd->erasesize=131072 devinfo.iowidth=8

..============================================

Ralink UBoot Version: 5.0.0.0

--------------------------------------------

ASIC MT7621A DualCore (MAC to MT7530 Mode)

DRAM_CONF_FROM: Auto-Detection

DRAM_TYPE: DDR3

DRAM bus: 16 bit

Xtal Mode=3 OCP Ratio=1/3

Flash component: NAND Flash

Date:Sep 25 2018 Time:12:04:25

============================================

icache: sets:256, ways:4, linesz:32 ,total:32768

dcache: sets:256, ways:4, linesz:32 ,total:32768

##### The CPU freq = 880 MHZ ####

estimate memory size =256 Mbytes

#Reset_MT7530

set LAN/WAN LLLLW

Please choose the operation:

1: Load system code to SDRAM via TFTP.

2: Load system code then write to Flash via TFTP.

3: Boot system code via Flash (default).

4: Entr boot command line interface.

7: Load Boot Loader code then write to Flash via Serial.

9: Load Boot Loader code then write to Flash via TFTP. 0

Booting System 2

..ranand_erase: start:40000, len:20000

..Done!

done

3: System Boot system code via Flash.

## Booting image at bc600000 ...

Image Name: MIPS OpenWrt Linux-4.14.103

Image Type: MIPS Linux Kernel Image (lzma compressed)

Data Size: 1906808 Bytes = 1.8 MB

Load Address: 80001000

Entry Point: 80001000

.............................. Verifying Checksum ... OK

Uncompressing Kernel Image ... OK

commandline uart_en=0 factory_mode=0 usb_u3=0

No initrd

## Transferring control to Linux (at address 80001000) ...

## Giving linux memsize in MB, 256

Starting kernel ...

[ 0.000000] Linux version 4.14.103 (ilyas@fish) (gcc version 7.4.0 (OpenWrt GCC 7.4.0 r9331-db5a1e49d6)) #0 SMP Fri Mar 1 14:19:36 2019

[ 0.000000] SoC Type: MediaTek MT7621 ver:1 eco:3

[ 0.000000] bootconsole [early0] enabled

[ 0.000000] CPU0 revision is: 0001992f (MIPS 1004Kc)

[ 0.000000] MIPS: machine is Xiaomi Mi Router 3 Pro

[ 0.000000] Determined physical RAM map:

[ 0.000000] memory: 1c000000 @ 00000000 (usable)

[ 0.000000] memory: 04000000 @ 20000000 (usable)

[ 0.000000] Initrd not found or empty - disabling initrd

[ 0.000000] VPE topology {2,2} total 4

[ 0.000000] Primary instruction cache 32kB, VIPT, 4-way, linesize 32 bytes.

[ 0.000000] Primary data cache 32kB, 4-way, PIPT, no aliases, linesize 32 bytes

[ 0.000000] MIPS secondary cache 256kB, 8-way, linesize 32 bytes.

[ 0.000000] Zone ranges:

[ 0.000000] Normal [mem 0x0000000000000000-0x000000000fffffff]

[ 0.000000] HighMem [mem 0x0000000010000000-0x0000000023ffffff]

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x0000000000000000-0x000000001bffffff]

[ 0.000000] node 0: [mem 0x0000000020000000-0x0000000023ffffff]

[ 0.000000] Initmem setup node 0 [mem 0x0000000000000000-0x0000000023ffffff]

[ 0.000000] random: get_random_bytes called from start_kernel+0x90/0x4a4 with crng_init=0

[ 0.000000] percpu: Embedded 14 pages/cpu @81491000 s26192 r8192 d22960 u57344

[ 0.000000] Built 1 zonelists, mobility grouping on. Total pages: 130560

[ 0.000000] Kernel command line: console=ttyS0,115200n8 rootfstype=squashfs,jffs2

[ 0.000000] PID hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.000000] Dentry cache hash table entries: 32768 (order: 5, 131072 bytes)

[ 0.000000] Inode-cache hash table entries: 16384 (order: 4, 65536 bytes)

[ 0.000000] Writing ErrCtl register=00000002

[ 0.000000] Readback ErrCtl register=00000002

[ 0.000000] Memory: 512944K/524288K available (4499K kernel code, 228K rwdata, 1000K rodata, 212K init, 248K bss, 11344K reserved, 0K cma-reserved, 262144K highmem)

[ 0.000000] SLUB: HWalign=32, Order=0-3, MinObjects=0, CPUs=4, Nodes=1

[ 0.000000] Hierarchical RCU implementation.

[ 0.000000] NR_IRQS: 256

[ 0.000000] CPU Clock: 880MHz

[ 0.000000] clocksource: GIC: mask: 0xffffffffffffffff max_cycles: 0xcaf478abb4, max_idle_ns: 440795247997 ns

[ 0.000000] clocksource: MIPS: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 4343773742 ns

[ 0.000009] sched_clock: 32 bits at 440MHz, resolution 2ns, wraps every 4880645118ns

[ 0.007818] Calibrating delay loop... 586.13 BogoMIPS (lpj=2930688)

[ 0.073982] pid_max: default: 32768 minimum: 301

[ 0.078754] Mount-cache hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.085263] Mountpoint-cache hash table entries: 1024 (order: 0, 4096 bytes)

[ 0.094104] Hierarchical SRCU implementation.

[ 0.099284] smp: Bringing up secondary CPUs ...

[ 0.104810] Primary instruction cache 32kB, VIPT, 4-way, linesize 32 bytes.

[ 0.104820] Primary data cache 32kB, 4-way, PIPT, no aliases, linesize 32 bytes

[ 0.104832] MIPS secondary cache 256kB, 8-way, linesize 32 bytes.

[ 0.104972] CPU1 revision is: 0001992f (MIPS 1004Kc)

[ 0.164041] Synchronize counters for CPU 1: done.

[ 0.198762] Primary instruction cache 32kB, VIPT, 4-way, linesize 32 bytes.

[ 0.198771] Primary data cache 32kB, 4-way, PIPT, no aliases, linesize 32 bytes

[ 0.198778] MIPS secondary cache 256kB, 8-way, linesize 32 bytes.

[ 0.198850] CPU2 revision is: 0001992f (MIPS 1004Kc)

[ 0.255250] Synchronize counters for CPU 2: done.

[ 0.286026] Primary instruction cache 32kB, VIPT, 4-way, linesize 32 bytes.

[ 0.286035] Primary data cache 32kB, 4-way, PIPT, no aliases, linesize 32 bytes

[ 0.286043] MIPS secondary cache 256kB, 8-way, linesize 32 bytes.

[ 0.286126] CPU3 revision is: 0001992f (MIPS 1004Kc)

[ 0.340429] Synchronize counters for CPU 3: done.

[ 0.370295] smp: Brought up 1 node, 4 CPUs

[ 0.378207] clocksource: jiffies: mask: 0xffffffff max_cycles: 0xffffffff, max_idle_ns: 19112604462750000 ns

[ 0.388007] futex hash table entries: 1024 (order: 3, 32768 bytes)

[ 0.394311] pinctrl core: initialized pinctrl subsystem

[ 0.400846] NET: Registered protocol family 16

[ 0.415257] PCI: assigned irq 23

[ 0.418409] PCI: assigned irq 24

[ 0.421652] PCI: assigned irq 25

[ 0.424792] pull PCIe RST: RALINK_RSTCTRL = 4000000

[ 0.729995] release PCIe RST: RALINK_RSTCTRL = 7000000

[ 0.735038] ***** Xtal 40MHz *****

[ 0.738399] release PCIe RST: RALINK_RSTCTRL = 7000000

[ 0.743498] Port 0 N_FTS = 1b102800

[ 0.746966] Port 1 N_FTS = 1b102800

[ 0.750408] Port 2 N_FTS = 1b102800

[ 1.905513] PCIE2 no card, disable it(RST&CLK)

[ 1.909874] -> 21007f2

[ 1.912276] PCIE0 enabled

[ 1.914867] PCIE1 enabled

[ 1.917471] PCI host bridge /pcie@1e140000 ranges:

[ 1.922254] MEM 0x0000000060000000..0x000000006fffffff

[ 1.927400] IO 0x000000001e160000..0x000000001e16ffff

[ 1.932598] PCI coherence region base: 0xbfbf8000, mask/settings: 0x60000000

[ 1.948930] mt7621_gpio 1e000600.gpio: registering 32 gpios

[ 1.954766] mt7621_gpio 1e000600.gpio: registering 32 gpios

[ 1.960480] mt7621_gpio 1e000600.gpio: registering 32 gpios

[ 1.968128] PCI host bridge to bus 0000:00

[ 1.972165] pci_bus 0000:00: root bus resource [mem 0x60000000-0x6fffffff]

[ 1.979022] pci_bus 0000:00: root bus resource [io 0xffffffff]

[ 1.984849] pci_bus 0000:00: root bus resource [??? 0x00000000 flags 0x0]

[ 1.991608] pci_bus 0000:00: No busn resource found for root bus, will use [bus 00-ff]

[ 2.000277] pci 0000:00:00.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 2.008212] pci 0000:00:01.0: bridge configuration invalid ([bus 00-00]), reconfiguring

[ 2.017459] pci 0000:00:00.0: BAR 0: no space for [mem size 0x80000000]

[ 2.024008] pci 0000:00:00.0: BAR 0: failed to assign [mem size 0x80000000]

[ 2.030883] pci 0000:00:01.0: BAR 0: no space for [mem size 0x80000000]

[ 2.037466] pci 0000:00:01.0: BAR 0: failed to assign [mem size 0x80000000]

[ 2.044367] pci 0000:00:00.0: BAR 8: assigned [mem 0x60000000-0x600fffff]

[ 2.051123] pci 0000:00:01.0: BAR 8: assigned [mem 0x60100000-0x601fffff]

[ 2.057842] pci 0000:00:00.0: BAR 1: assigned [mem 0x60200000-0x6020ffff]

[ 2.064604] pci 0000:00:01.0: BAR 1: assigned [mem 0x60210000-0x6021ffff]

[ 2.071325] pci 0000:01:00.0: BAR 0: assigned [mem 0x60000000-0x600fffff 64bit]

[ 2.078604] pci 0000:00:00.0: PCI bridge to [bus 01]

[ 2.083506] pci 0000:00:00.0: bridge window [mem 0x60000000-0x600fffff]

[ 2.090273] pci 0000:02:00.0: BAR 0: assigned [mem 0x60100000-0x601fffff 64bit]

[ 2.097507] pci 0000:00:01.0: PCI bridge to [bus 02]

[ 2.102441] pci 0000:00:01.0: bridge window [mem 0x60100000-0x601fffff]

[ 2.110509] clocksource: Switched to clocksource GIC

[ 2.117130] NET: Registered protocol family 2

[ 2.122072] TCP established hash table entries: 2048 (order: 1, 8192 bytes)

[ 2.128956] TCP bind hash table entries: 2048 (order: 2, 16384 bytes)

[ 2.135410] TCP: Hash tables configured (established 2048 bind 2048)

[ 2.141821] UDP hash table entries: 256 (order: 1, 8192 bytes)

[ 2.147582] UDP-Lite hash table entries: 256 (order: 1, 8192 bytes)

[ 2.154064] NET: Registered protocol family 1

[ 2.390458] 4 CPUs re-calibrate udelay(lpj = 2924544)

[ 2.397018] Crashlog allocated RAM at address 0x3f00000

[ 2.402429] workingset: timestamp_bits=30 max_order=17 bucket_order=0

[ 2.416158] squashfs: version 4.0 (2009/01/31) Phillip Lougher

[ 2.421958] jffs2: version 2.2 (NAND) (SUMMARY) (LZMA) (RTIME) (CMODE_PRIORITY) (c) 2001-2006 Red Hat, Inc.

[ 2.433632] random: fast init done

[ 2.438056] bounce: pool size: 64 pages

[ 2.441917] io scheduler noop registered

[ 2.445741] io scheduler deadline registered (default)

[ 2.451836] Serial: 8250/16550 driver, 3 ports, IRQ sharing disabled

[ 2.459383] console [ttyS0] disabled

[ 2.463006] 1e000c00.uartlite: ttyS0 at MMIO 0x1e000c00 (irq = 18, base_baud = 3125000) is a 16550A

[ 2.472021] console [ttyS0] enabled

[ 2.472021] console [ttyS0] enabled

[ 2.478874] bootconsole [early0] disabled

[ 2.478874] bootconsole [early0] disabled

[ 2.487665] cacheinfo: Unable to detect cache hierarchy for CPU 0

[ 2.494610] MediaTek Nand driver init, version v2.1 Fix AHB virt2phys error

[ 2.501745] Enable NFI Clock

[ 2.504617] # MTK NAND # : Use HW ECC

[ 2.508278] Device found in MTK table, ID: c8da, EXT_ID: 909544

[ 2.514194] Support this Device in MTK table! c8da

[ 2.519143] [NAND]select ecc bit:4, sparesize :64 spare_per_sector=16

[ 2.525618] nand: device found, Manufacturer ID: 0xc8, Chip ID: 0xda

[ 2.531951] nand: ESMT NAND 256MiB 3,3V 8-bit

[ 2.536287] nand: 256 MiB, SLC, erase size: 128 KiB, page size: 2048, OOB size: 64

[ 2.543852] Scanning device for bad blocks

[ 2.831787] 10 fixed-partitions partitions found on MTD device MT7621-NAND

[ 2.838629] Creating 10 MTD partitions on "MT7621-NAND":

[ 2.843940] 0x000000000000-0x000000040000 : "Bootloader"

[ 2.850313] 0x000000040000-0x000000080000 : "Config"

[ 2.856328] 0x000000080000-0x0000000c0000 : "Bdata"

[ 2.862255] 0x0000000c0000-0x000000100000 : "Factory"

[ 2.868321] 0x000000100000-0x000000140000 : "crash"

[ 2.874239] 0x000000140000-0x0000001c0000 : "crash_syslog"

[ 2.880851] 0x0000001c0000-0x000000200000 : "reserved0"

[ 2.887070] 0x000000200000-0x000000600000 : "kernel_stock"

[ 2.893623] 0x000000600000-0x000000a00000 : "kernel"

[ 2.899613] 0x000000a00000-0x00000ff80000 : "ubi"

[ 2.907250] [mtk_nand] probe successfully!

[ 2.912079] Signature matched and data read!

[ 2.916327] load_fact_bbt success 2047

[ 2.920913] libphy: Fixed MDIO Bus: probed

[ 2.993056] libphy: mdio: probed

[ 4.396752] mtk_soc_eth 1e100000.ethernet: loaded mt7530 driver

[ 4.403465] mtk_soc_eth 1e100000.ethernet eth0: mediatek frame engine at 0xbe100000, irq 21

[ 4.414283] NET: Registered protocol family 10

[ 4.420123] Segment Routing with IPv6

[ 4.423950] NET: Registered protocol family 17

[ 4.428421] 8021q: 802.1Q VLAN Support v1.8

[ 4.435707] UBI: auto-attach mtd9

[ 4.439045] ubi0: attaching mtd9

[ 6.795085] ubi0: scanning is finished

[ 6.816050] ubi0: attached mtd9 (name "ubi", size 245 MiB)

[ 6.821554] ubi0: PEB size: 131072 bytes (128 KiB), LEB size: 126976 bytes

[ 6.828394] ubi0: min./max. I/O unit sizes: 2048/2048, sub-page size 2048

[ 6.835160] ubi0: VID header offset: 2048 (aligned 2048), data offset: 4096

[ 6.842100] ubi0: good PEBs: 1964, bad PEBs: 0, corrupted PEBs: 0

[ 6.848164] ubi0: user volume: 0, internal volumes: 1, max. volumes count: 128

[ 6.855364] ubi0: max/mean erase counter: 3/1, WL threshold: 4096, image sequence number: 281942099

[ 6.864379] ubi0: available PEBs: 1920, total reserved PEBs: 44, PEBs reserved for bad PEB handling: 40

[ 6.873764] ubi0: background thread "ubi_bgt0d" started, PID 370

[ 6.873792] hctosys: unable to open rtc device (rtc0)

[ 6.885042] usb_vbus: disabling

[ 6.888774] VFS: Cannot open root device "(null)" or unknown-block(0,0): error -6

[ 6.896255] Please append a correct "root=" boot option; here are the available partitions:

[ 6.904591] 1f00 256 mtdblock0

[ 6.904597] (driver?)

[ 6.911112] 1f01 256 mtdblock1

[ 6.911117] (driver?)

[ 6.917618] 1f02 256 mtdblock2

[ 6.917622] (driver?)

[ 6.924136] 1f03 256 mtdblock3

[ 6.924140] (driver?)

[ 6.930654] 1f04 256 mtdblock4

[ 6.930658] (driver?)

[ 6.937159] 1f05 512 mtdblock5

[ 6.937163] (driver?)

[ 6.943677] 1f06 256 mtdblock6

[ 6.943682] (driver?)

[ 6.950181] 1f07 4096 mtdblock7

[ 6.950185] (driver?)

[ 6.956699] 1f08 4096 mtdblock8

[ 6.956704] (driver?)

[ 6.963218] 1f09 251392 mtdblock9

[ 6.963223] (driver?)

[ 6.969722] Kernel panic - not syncing: VFS: Unable to mount root fs on unknown-block(0,0)

[ 6.979941] Rebooting in 1 seconds..

@pellmen haha... congratulations on your new UART! is this what you finally see was going on while the thing was bootlooping? do you know how to use tftpboot? (it's easy once you configure the tftpd server... select '1' in the uboot menu, and use the initramfs-kernel.bin file to boot ... once you've got it up, you can do 'mtd write' again).... sorry the build was bad (again), but knowing that the build was bad, i think this was just a transient problem that won't repeat.

btw, if you're too lazy/bored to setup a tftpd server, you can also press '4' at the uboot menu, and set the flag_try_sys1_failed = 0 flag_try_sys2_failed = 1 (and then save) and reboot into stock recovery (with stock firmware on a usb)... IIRC the syntax is

setenv flag_try_sys1_failed 0

setenv flag_try_sys2_failed 1

saveenv

reset

good luck, and sorry again for the mess-up..

EDIT: just for sanity/safety's sake, you might also want to do mtd erase on all the partitions you won't be writing to completely (as in, coming from stock: rootfs0, rootfs1, overlay... coming from one of my releases, 'ubi')

I'm just learning how to do this😄

@pellmen it's well worth the effort  much easier to sanity-test a release too (and much less stressful to test new bits when you know you can always recover)

much easier to sanity-test a release too (and much less stressful to test new bits when you know you can always recover)

initramf is ok))) router is alive)))

@pellmen hurrah! and now you have learned yet another extremely useful skill!  (and you know what the mystical initramfs file is for too ;))

(and you know what the mystical initramfs file is for too ;))

@pellmen ... soo... everything normal? internet speed is OK? no more panic bootloops?

Updating this page

@ilyas, yes, all's ok)) I've earned some scheme on mt7615, you can see it here, if you now how to work with *.dsn https://drive.google.com/folderview?id=1-0JlyhbCR8p-jia3POgmnOVvXuhrWOyJ

@pellmen no i have no idea what .dsn files are  never learned much about hardware...

never learned much about hardware...

btw, i'm curious what speeds you're getting with the r3p... same as stock? how about compared to rc1?

i've put rc1+mt7615e-2 into "production" (gulp...) now if it does something stupid i'll have 50 people yelling at me....

@ilyas, unfortunatly i'm not at home now and can't test it. I've added pdf to previous post with scheme of mt7615 2.4Ghz))) it was so hard to get all these files, becase they cost from 2 to 4 "rd" (the currency of chinees forum to download them). So i had to post leaked 5.0.2.0 driver (they don't have it yet) and wait someone to download it😄 and I finaly get all stuff from that forum))) if somebody interested - here's my theme on chinees forum)

Rather you than me lol..

The wiki is almost done. People can add finishing touch to those. I've filled in most of the items.

https://openwrt.org/inbox/xiaomi/xiaomi_r3p_pro#info

@ilyas @PeLLmEn Please check the install instructions in the wiki and edit them if necessary.

Thanks man..

@pellmen funny you "sold" them the 5.0.2.0 driver in exchange for the schematics

@ilyas it was the only way to earn schematics)))

@pellmen i have a favor to ask you... this "panic with micron chip" we had earlier is bothering me... i've hoped I could track it down to a bug in my code (or somewhere) but it just doesn't make sense. I've seen the posts on 4pda, about how a custom pandorabox build worked, but that doesn't really make sense to me either (ie, needing to modify uboot seems strange).

looking at the bootlogs (https://4pda.ru/forum/index.php?showtopic=810698&view=findpost&p=82662335) and particularly the bit where it prints out the mtd partition table, it looks like they end the partition table at 0x00000f200000 while on my bits I end the partition table at 0x00000ff80000 ... I wonder if that's the trick to get it to work on Micron chips (ie, end the partition table early). (BTW, one "technical document" talks about reserving 2% of space for bad blocks... -2% of 256MB would end us around 0xfa00000 (which is still earlier than 0xf200000)...

so now for my "favor"... I really want to make "openwrt on mir3p" a success (i don't know if you can tell already)... and it irks me to know that users with micron chips won't be able to install my bits (at least it seems that way)... do you think "skull999666" (who reported the panic) or "toikvl" (apparently he also has a micron chip) would be able to help out (since I don't have one I can test with)...

what I'd like to see (perhaps most importantly) is the bootlog from "stock" xiaomi firmware booting the mir3p with a micron chip... I want to know where the mtd table ends on stock/micron... and if it ends somewhere different (like 0xf200000), if they would be willing to test custom bits? i got the official go-ahead to release two versions (for the ESMT chip and for the Micron chip) of openwrt/mir3p but I first want to see if I can figure out what's wrong.

I guess I could post to 4pda but I'm shy because I don't speak russian  and i don't know anyone there.. but if you think it's best for me to post there directly, I'll do that.

and i don't know anyone there.. but if you think it's best for me to post there directly, I'll do that.