No luck with pressing keys. I can see that keystrokes are going to terminal screen via ttl serial. (without tx pin there is no output characters so I'm pretty sure that USB TTL cable works.) It seems that the default option 3 timeout is too short or fixed value. Anyway it's impossible to choose anything.

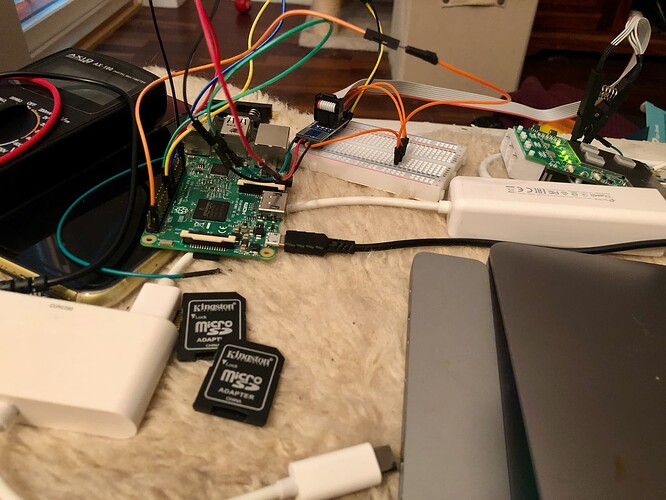

I just got SOIC-8 clip and after all it seems to work with Raspberry Pi:

sippe@raspberrypi:~ $ flashrom -p linux_spi:dev=/dev/spidev0.0,spispeed=2000 -V

...

===

SFDP has autodetected a flash chip which is not natively supported by flashrom yet.

All standard operations (read, verify, erase and write) should work, but to support all possible features we need to add them manually.

You can help us by mailing us the output of the following command to flashrom@flashrom.org:

'flashrom -VV [plus the -p/--programmer parameter]'

Thanks for your help!

===

Found Unknown flash chip "SFDP-capable chip" (8192 kB, SPI) on linux_spi.

Probing for AMIC unknown AMIC SPI chip, 0 kB: probe_spi_rdid_generic: id1 0x20, id2 0x7017

Probing for Atmel unknown Atmel SPI chip, 0 kB: probe_spi_rdid_generic: id1 0x20, id2 0x7017

Probing for Eon unknown Eon SPI chip, 0 kB: probe_spi_rdid_generic: id1 0x20, id2 0x7017

Probing for Macronix unknown Macronix SPI chip, 0 kB: probe_spi_rdid_generic: id1 0x20, id2 0x7017

Probing for PMC unknown PMC SPI chip, 0 kB: probe_spi_rdid_generic: id1 0x20, id2 0x7017

Probing for SST unknown SST SPI chip, 0 kB: probe_spi_rdid_generic: id1 0x20, id2 0x7017

Probing for ST unknown ST SPI chip, 0 kB: probe_spi_rdid_generic: id1 0x20, id2 0x7017

Probing for Sanyo unknown Sanyo SPI chip, 0 kB: probe_spi_rdid_generic: id1 0x20, id2 0x7017

Probing for Winbond unknown Winbond (ex Nexcom) SPI chip, 0 kB: probe_spi_rdid_generic: id1 0x20, id2 0x7017

Probing for Generic unknown SPI chip (RDID), 0 kB: probe_spi_rdid_generic: id1 0x20, id2 0x7017

Probing for Generic unknown SPI chip (REMS), 0 kB: probe_spi_rems: id1 0x20, id2 0x16

Found Unknown flash chip "SFDP-capable chip" (8192 kB, SPI).

No operations were specified.

At the moment I am little lost because I don't have clever idea how to make correct flash operation so I'm asking help to make correct steps with flashrom.

Reading works fine:

sippe@raspberrypi:~ $ flashrom -p linux_spi:dev=/dev/spidev0.0,spispeed=2000 -r bricked_tp-link.bin

flashrom v1.2 on Linux 5.15.32-v8+ (aarch64)

flashrom is free software, get the source code at https://flashrom.org

Using clock_gettime for delay loops (clk_id: 1, resolution: 1ns).

===

SFDP has autodetected a flash chip which is not natively supported by flashrom yet.

All standard operations (read, verify, erase and write) should work, but to support all possible features we need to add them manually.

You can help us by mailing us the output of the following command to flashrom@flashrom.org:

'flashrom -VV [plus the -p/--programmer parameter]'

Thanks for your help!

===

Found Unknown flash chip "SFDP-capable chip" (8192 kB, SPI) on linux_spi.

Reading flash... done.

If I try to write something flashrom says that binary file is too small:

sippe@raspberrypi:~ $ flashrom -p linux_spi:dev=/dev/spidev0.0,spispeed=2000 -w openwrt-ramips-mt7621-tplink_tl-wpa8631p-v3-squashfs-factory.bin

flashrom v1.2 on Linux 5.15.32-v8+ (aarch64)

flashrom is free software, get the source code at https://flashrom.org

Using clock_gettime for delay loops (clk_id: 1, resolution: 1ns).

===

SFDP has autodetected a flash chip which is not natively supported by flashrom yet.

All standard operations (read, verify, erase and write) should work, but to support all possible features we need to add them manually.

You can help us by mailing us the output of the following command to flashrom@flashrom.org:

'flashrom -VV [plus the -p/--programmer parameter]'

Thanks for your help!

===

Found Unknown flash chip "SFDP-capable chip" (8192 kB, SPI) on linux_spi.

Error: Image size (6617623 B) doesn't match the flash chip's size (8388608 B)!

You asked how I bricked my device. Well... It was stupid brainfart. I tried to install ssl-luci and it was too big to write to flash drive. Then I wondered that easiest way is flash openwrt-ramips-mt7621-tplink_tl-wpa8631p-v3-squashfs-factory.bin again via command line and now I am here with my tiny and cute bricked device.

Here is the setup at the moment: