Hello!

Sorry, could you help me. I did not understand which registers to use to enable RGMII2 on the MT7621 processor? In my case, an external PHY RTL8211DN is connected to the MT7621 processor.

Hi @telecom21, Which device are you using?

Enabling RGMII2 is not enough. You have to know if the phy talks tot the switch or the cpu.

I think that you can see that with the original software and command "ip link".

Do you may have a dmesg output?

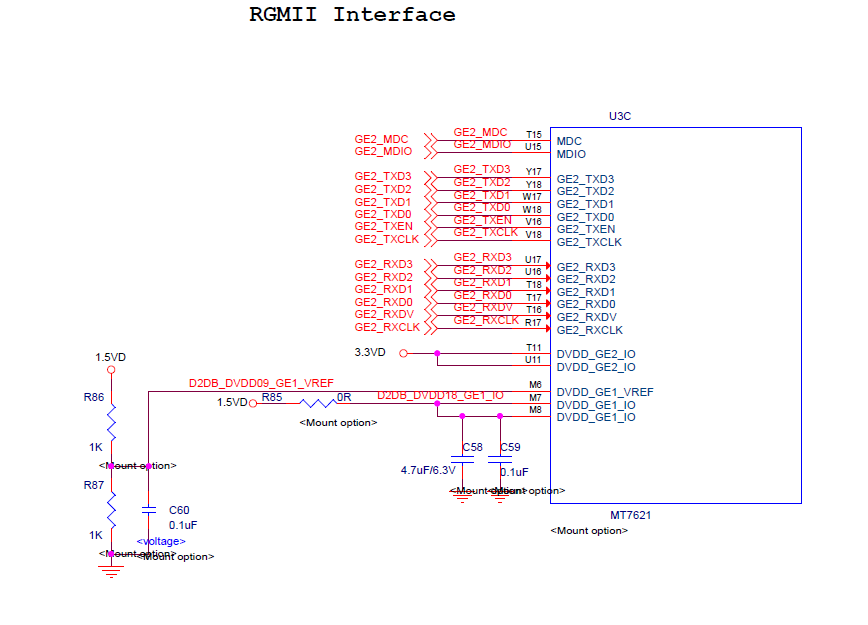

I have my own original device. A bit like Mqmaker WITI. I look at the RGMII interface with an oscilloscope and see the signals from the PHY side. On the processor side, I was able to achieve only the output of the GE2_TXCLK signal - by writing the value 0x2107Е33В to the GE2_MAC_CONTROL register (address 0x1Е110200). I don’t understand how to connect RGMII2 to the 5th port of MT7530.

@telecom21 So you made your own PCB? This mean you have a schematic?

You have to remember that the 2nd GMAC, switch port 5 and external phy share the same RGMII2 bus.

Depending on how the phy txd and rxd pins are connected to the soc. the phy can only talk to the 2nd GMAC or port 5. Read this for extra information: https://git.kernel.org/pub/scm/linux/kernel/git/torvalds/linux.git/commit/?h=v5.4-rc3&id=4f358cbd054d905329718443a4dd781d26ea1079

So MT7621 GE2_TXDx are connected to the TXDx pins of the phy? That means that the phy can only talks to the 2nd GMAC. RGMII2 pins have to me set-up as RGMII mode. port 5 of the switch must be disabled which is by default.

Which kernel are you using?

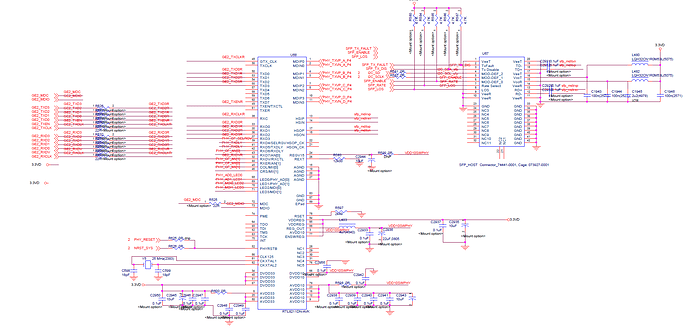

Yes, we ourselves made a circuit and a printed circuit board (I pin the connection diagram).

So far I have not used your patches with DSA. I use the standard driver in my project (https://github.com/openwrt/openwrt/tree/master/target/linux/ramips/files-4.14/drivers/net/ethernet/mediatek).

@telecom21 Thanks for sharing this information.

I am not sure if current openwrt driver supports the 2nd GMAC properly.

It is still on my todo list to add port 5 support to openwrt kernel.

I only know if you are using my driver 2nd GMAC is working.

This is an example branch which support ER-X-SFP with phylink and SFP port.

Device tree files are found here: https://github.com/vDorst/linux-1/tree/net-next-phylink-upstream-merge-wr1201/drivers/staging/mt7621-dts

If you build openwrt with the config option

CONFIG_TARGET_ROOTFS_CPIOGZ=y

it generated a bin/targets/ramips/mt7621/openwrt-ramips-mt7621-rootfs.cpio.gz

This file can be included in the kernel uImage file with the kernel config option

CONFIG_INITRAMFS_SOURCE="openwrt-ramips-mt7621-rootfs.cpio.gz"

Now you can directly tftp uImage image and boot it.

So you have a kernel and full working openwrt system.

Thank!!!

Is the PHY connection diagram correct?

@telecom21 It seems correct.

Based of the schematic, device will get shared wan (SFP/RJ45) port and 5 lan ports?

Yes. And what values of the registers MHWTRAP (0x7804) and PMCR_P5 (0x3500) should be?

HWTRAP[7804]: 0x17c4f

PMCR_P5 = 0x8000 (Forced mode, disables everything)

Hi

I really appriciate your design, I am following your sketch to design my own pcbs-assembly and for this a little help from your end is required, can you please share your email or revert back to my email.

Sandeep.akmboj86@gmail.com

Looking forward to work with you

Regards

Sandeep

Hello!

You can email me konovalov_vladimir@live.ru

This topic was automatically closed 10 days after the last reply. New replies are no longer allowed.