kernel 4.4?

i know i'm able to compile openwrt 22.03.3 with this drivers but only for nand . it work for xiaomi ax 1800 series, but not for nor device. do you have the proprietary dts of this nor devices?

dts are in dts folders

for zbt-z100 ax

i can find with opkg install dtc

dtc -I fs /proc/device-tree > dts.txt

/dts-v1/;

/ {

model = "MediaTek MT7621 RFB (802.11ax,SNOR)";

compatible = "mediatek,mt7621-rfb-nor", "mediatek,mt7621-soc";

#address-cells = <0x1>;

#size-cells = <0x1>;

gsw {

mediatek,mdio = <0xb>;

interrupts = <0x0 0x17 0x4>;

mediatek,mcm;

compatible = "mediatek,mt753x";

mt7530,direct-phy-access;

reset-names = "mcm";

mediatek,portmap = "llllw";

resets = <0x3 0x2>;

#address-cells = <0x1>;

#size-cells = <0x0>;

interrupt-parent = <0x1>;

port@5 {

reg = <0x5>;

compatible = "mediatek,mt753x-port";

phy-mode = "rgmii";

fixed-link {

full-duplex;

speed = <0x3e8>;

};

};

port@6 {

reg = <0x6>;

compatible = "mediatek,mt753x-port";

phy-mode = "trgmii";

fixed-link {

full-duplex;

speed = <0x3e8>;

};

};

mdio-bus {

#address-cells = <0x1>;

#size-cells = <0x0>;

};

};

pcie@1e140000 {

reg = <0x1e140000 0x40000>;

interrupts = <0x0 0x4 0x4 0x0 0x18 0x4 0x0 0x19 0x4>;

pinctrl-0 = <0xd>;

compatible = "mediatek,mt7621-pci";

clock-names = "pcie0", "pcie1", "pcie2";

reset-gpios = <0xf 0x13 0x1>;

reset-names = "pcie0", "pcie1", "pcie2";

bus-range = <0x0 0xff>;

device_type = "pci";

clocks = <0xe 0x18 0xe 0x19 0xe 0x1a>;

reset-gpio-names = "pcie";

ranges = <0x2000000 0x0 0x0 0x60000000 0x0 0x10000000 0x1000000 0x0 0x0 0x1e160000 0x0 0x10000>;

resets = <0x3 0x18 0x3 0x19 0x3 0x1a>;

status = "okay";

#address-cells = <0x3>;

#size-cells = <0x2>;

pinctrl-names = "default";

interrupt-parent = <0x1>;

pcie0 {

reg = <0x0 0x0 0x0 0x0 0x0>;

device_type = "pci";

#address-cells = <0x3>;

#size-cells = <0x2>;

};

pcie1 {

reg = <0x800 0x0 0x0 0x0 0x0>;

device_type = "pci";

#address-cells = <0x3>;

#size-cells = <0x2>;

};

pcie2 {

reg = <0x1000 0x0 0x0 0x0 0x0>;

device_type = "pci";

#address-cells = <0x3>;

#size-cells = <0x2>;

};

};

cpus {

cpu@0 {

compatible = "mips,mips1004Kc";

};

cpu@1 {

compatible = "mips,mips1004Kc";

};

};

crypto@1e004000 {

reg = <0x1e004000 0x1000>;

interrupts = <0x0 0x13 0x4>;

compatible = "mediatek,mtk-eip93";

status = "okay";

interrupt-parent = <0x1>;

};

sdhci@1e130000 {

reg = <0x1e130000 0x4000>;

interrupts = <0x0 0x14 0x4>;

pinctrl-0 = <0xc>;

compatible = "mediatek,mt7621-sdhci";

status = "okay";

pinctrl-names = "default";

interrupt-parent = <0x1>;

};

usb-phy@1e1d0000 {

reg = <0x1e1d0000 0x300>;

compatible = "mediatek,mt7621-u3phy", "mediatek,mt2701-u3phy";

ranges;

status = "okay";

#address-cells = <0x1>;

#size-cells = <0x1>;

usb-phy@0x1e1d0800 {

reg = <0x1e1d0800 0x100>;

clock-names = "ref";

#phy-cells = <0x1>;

clocks = <0x10>;

phandle = <0x11>;

linux,phandle = <0x11>;

};

usb-phy@0x1e1d0900 {

reg = <0x1e1d0900 0x700>;

clock-names = "ref";

#phy-cells = <0x1>;

clocks = <0x10>;

phandle = <0x12>;

linux,phandle = <0x12>;

};

usb-phy@0x1e1d1000 {

reg = <0x1e1d1000 0x100>;

clock-names = "ref";

#phy-cells = <0x1>;

clocks = <0x10>;

phandle = <0x13>;

linux,phandle = <0x13>;

};

};

hnat@1e100000 {

reg = <0x1e100000 0x3000>;

mtketh-ppd = "eth0";

mtketh-wan = "eth1";

compatible = "mediatek,mtk-hnat_v1";

reset-names = "mtketh";

resets = <0xa 0x0>;

status = "okay";

ext-devices = "rax0", "ra0", "rax1", "ra1", "rax2", "ra2", "rax3", "ra3", "apclix0", "apcli0";

mtketh-max-gmac = <0x2>;

};

rstctrl {

#reset-cells = <0x1>;

compatible = "ralink,rt2880-reset";

phandle = <0x3>;

linux,phandle = <0x3>;

};

sysclock50M@0 {

#clock-cells = <0x0>;

compatible = "fixed-clock";

clock-frequency = <0x2faf080>;

phandle = <0x7>;

linux,phandle = <0x7>;

};

apll@0 {

#clock-cells = <0x0>;

compatible = "fixed-clock";

clock-frequency = <0x1017df80>;

phandle = <0x2>;

linux,phandle = <0x2>;

};

chosen {

bootargs = "console=ttyS0,115200";

};

raeth@1e100000 {

reg = <0x1e100000 0xe000>;

interrupts = <0x0 0x3 0x4>;

compatible = "mediatek,mt7621-eth";

status = "disabled";

mediatek,ethsys = <0xa>;

interrupt-parent = <0x1>;

};

gpio-keys-polled {

compatible = "gpio-keys-polled";

poll-interval = <0x14>;

#address-cells = <0x1>;

#size-cells = <0x0>;

mesh {

gpios = <0xf 0xf 0x1>;

label = "mesh";

linux,code = <0x198>;

};

reset {

gpios = <0xf 0x12 0x1>;

label = "reset";

linux,code = <0x198>;

};

};

gpio-leds {

compatible = "gpio-leds";

red {

gpios = <0xf 0x4 0x0>;

label = "red";

};

blue {

gpios = <0xf 0x10 0x1>;

label = "blue";

};

green {

gpios = <0xf 0x3 0x1>;

label = "green";

};

};

palmbus@1e000000 {

reg = <0x1e000000 0x100000>;

compatible = "palmbus";

ranges = <0x0 0x1e000000 0xfffff>;

#address-cells = <0x1>;

#size-cells = <0x1>;

nand@3000 {

reg = <0x3000 0x800>;

pinctrl-0 = <0x9>;

ecc-engine = <0x8>;

compatible = "mediatek,mt7621-nfc";

status = "disabled";

#address-cells = <0x1>;

#size-cells = <0x1>;

pinctrl-names = "default";

};

i2s@a00 {

reg = <0xa00 0x100>;

dmas = <0x4 0x4 0x4 0x6>;

interrupts = <0x0 0x10 0x4>;

txdma-req = <0x2>;

compatible = "mediatek,mt7621-i2s";

reset-names = "i2s";

clocks = <0x2>;

resets = <0x3 0x11>;

status = "disabled";

rxdma-req = <0x3>;

dma-names = "tx", "rx";

interrupt-parent = <0x1>;

};

spi@b00 {

reg = <0xb00 0x100>;

pinctrl-0 = <0x6>;

compatible = "mediatek,mt7621-spi";

reset-names = "spi";

clocks = <0x5>;

resets = <0x3 0x12>;

status = "okay";

#address-cells = <0x1>;

#size-cells = <0x0>;

pinctrl-names = "default";

m25p80@0 {

reg = <0x0>;

compatible = "jedec,spi-nor";

m25p,chunked-io = <0x20>;

spi-max-frequency = <0x989680>;

#address-cells = <0x1>;

#size-cells = <0x1>;

partition@0 {

reg = <0x0 0x30000>;

label = "Bootloader";

};

partition@30000 {

reg = <0x30000 0x10000>;

label = "Config";

};

partition@50000 {

reg = <0x50000 0x40000>;

label = "Factory";

};

partition@90000 {

reg = <0x90000 0xf70000>;

label = "firmware";

};

};

};

uartlite@c00 {

reg = <0xc00 0x100>;

interrupts = <0x0 0x1a 0x4>;

reg-shift = <0x2>;

no-loopback-test;

compatible = "mediatek,mt6577-uart", "ns16550a";

clock-frequency = <0x2faf080>;

clocks = <0x7>;

reg-io-width = <0x4>;

interrupt-parent = <0x1>;

};

gdma@2800 {

reg = <0x2800 0x800>;

interrupts = <0x0 0xd 0x4>;

compatible = "mtk,rt3883-gdma";

reset-names = "dma";

#dma-requests = <0x10>;

resets = <0x3 0xe>;

status = "disabled";

#dma-channels = <0x10>;

#dma-cells = <0x1>;

phandle = <0x4>;

linux,phandle = <0x4>;

interrupt-parent = <0x1>;

};

sysc@0 {

reg = <0x0 0x100>;

compatible = "mtk,mt7621-sysc";

};

memc@5000 {

reg = <0x5000 0x1000>;

compatible = "mtk,mt7621-memc";

};

uartfull@d00 {

reg = <0xd00 0x100>;

interrupts = <0x0 0x1b 0x4>;

reg-shift = <0x2>;

no-loopback-test;

compatible = "mediatek,mt6577-uart", "ns16550a";

clock-frequency = <0x2faf080>;

clocks = <0x7>;

status = "okay";

reg-io-width = <0x4>;

interrupt-parent = <0x1>;

};

uartfull@e00 {

reg = <0xe00 0x100>;

interrupts = <0x0 0x1c 0x4>;

reg-shift = <0x2>;

no-loopback-test;

compatible = "mediatek,mt6577-uart", "ns16550a";

clock-frequency = <0x2faf080>;

clocks = <0x7>;

status = "okay";

reg-io-width = <0x4>;

interrupt-parent = <0x1>;

};

ecc@3800 {

reg = <0x3800 0x800>;

compatible = "mediatek,mt7621-ecc";

status = "disabled";

phandle = <0x8>;

linux,phandle = <0x8>;

};

wdt@100 {

reg = <0x100 0x100>;

compatible = "mtk,mt7621-wdt";

};

hsdma@7000 {

reg = <0x7000 0x1000>;

interrupts = <0x0 0xb 0x4>;

compatible = "mediatek,mt7621-hsdma";

reset-names = "hsdma";

#dma-requests = <0x1>;

resets = <0x3 0x5>;

status = "disabled";

#dma-channels = <0x1>;

#dma-cells = <0x1>;

interrupt-parent = <0x1>;

};

gpio@600 {

reg = <0x600 0x100>;

interrupts = <0x0 0xc 0x4>;

compatible = "mtk,mt7621-gpio";

#address-cells = <0x1>;

#size-cells = <0x0>;

interrupt-parent = <0x1>;

bank@0 {

reg = <0x0>;

#gpio-cells = <0x2>;

compatible = "mtk,mt7621-gpio-bank";

phandle = <0xf>;

gpio-controller;

linux,phandle = <0xf>;

};

bank@1 {

reg = <0x1>;

#gpio-cells = <0x2>;

compatible = "mtk,mt7621-gpio-bank";

gpio-controller;

};

bank@2 {

reg = <0x2>;

#gpio-cells = <0x2>;

compatible = "mtk,mt7621-gpio-bank";

gpio-controller;

};

};

};

ethernet@1e100000 {

reg = <0x1e100000 0xe000>;

interrupts = <0x0 0x3 0x4>;

compatible = "mediatek,mt7621-eth", "syscon";

status = "okay";

#address-cells = <0x1>;

#size-cells = <0x0>;

mediatek,ethsys = <0xa>;

interrupt-parent = <0x1>;

mac@0 {

reg = <0x0>;

compatible = "mediatek,eth-mac";

phy-mode = "trgmii";

fixed-link {

full-duplex;

pause;

speed = <0x3e8>;

};

};

mac@1 {

reg = <0x1>;

compatible = "mediatek,eth-mac";

phy-mode = "rgmii";

fixed-link {

full-duplex;

pause;

speed = <0x3e8>;

};

};

mdio-bus {

#address-cells = <0x1>;

phandle = <0xb>;

#size-cells = <0x0>;

linux,phandle = <0xb>;

ethernet-phy@1f {

reg = <0x1f>;

phy-mode = "rgmii";

};

};

};

sysclock125M@0 {

#clock-cells = <0x0>;

compatible = "fixed-clock";

clock-frequency = <0x7735940>;

phandle = <0x10>;

linux,phandle = <0x10>;

};

aliases {

serial0 = "/palmbus@1e000000/uartlite@c00";

};

interrupt-controller@1fbc0000 {

reg = <0x1fbc0000 0x2000>;

compatible = "mti,gic";

mti,reserved-cpu-vectors = <0x7>;

#interrupt-cells = <0x3>;

phandle = <0x1>;

interrupt-controller;

linux,phandle = <0x1>;

timer {

interrupts = <0x1 0x1 0x0>;

compatible = "mti,gic-timer";

clocks = <0x14>;

};

};

pinctrl {

pinctrl-0 = <0x15>;

compatible = "mtk,mtkmips-pinmux";

pinctrl-names = "default";

i2c {

i2c {

mtk,function = "gpio";

mtk,group = "i2c";

};

};

spi {

phandle = <0x6>;

linux,phandle = <0x6>;

spi {

mtk,function = "spi";

mtk,group = "spi";

};

};

mdio {

mdio {

mtk,function = "mdio";

mtk,group = "mdio";

};

};

nand {

phandle = <0x9>;

linux,phandle = <0x9>;

sdhci-nand {

mtk,function = "nand2";

mtk,group = "sdhci";

};

spi-nand {

mtk,function = "nand1";

mtk,group = "spi";

};

};

pcie {

phandle = <0xd>;

linux,phandle = <0xd>;

pcie {

mtk,function = "gpio";

mtk,group = "pcie";

};

};

sdhci {

phandle = <0xc>;

linux,phandle = <0xc>;

sdhci {

mtk,function = "sdhci";

mtk,group = "sdhci";

};

};

uart1 {

uart1 {

mtk,function = "uart1";

mtk,group = "uart1";

};

};

uart2 {

uart2 {

mtk,function = "uart2";

mtk,group = "uart2";

};

};

uart3 {

uart3 {

mtk,function = "uart3";

mtk,group = "uart3";

};

};

pinctrl0 {

phandle = <0x15>;

linux,phandle = <0x15>;

gpio {

mtk,function = "gpio";

mtk,group = "i2c", "jtag";

};

uart2 {

mtk,function = "uart2";

mtk,group = "uart2";

};

uart3 {

mtk,function = "uart3";

mtk,group = "uart3";

};

};

rgmii1 {

rgmii1 {

mtk,function = "rgmii1";

mtk,group = "rgmii1";

};

};

rgmii2 {

rgmii2 {

mtk,function = "rgmii2";

mtk,group = "rgmii2";

};

};

};

ethsys@1e000000 {

reg = <0x1e000000 0x8000>;

compatible = "mediatek,mt7621-ethsys", "syscon";

phandle = <0xa>;

linux,phandle = <0xa>;

};

usb@1e1c0000 {

reg = <0x1e1c0000 0x1000 0x1e1d0700 0x100>;

phys = <0x11 0x3 0x12 0x4 0x13 0x3>;

interrupts = <0x0 0x16 0x4>;

reg-names = "mac", "ippc";

compatible = "mediatek,mt7621-xhci", "mediatek,mt2701-xhci";

clock-names = "sys_ck", "free_ck", "ahb_ck", "dma_ck";

clocks = <0x10 0x10 0x10 0x10>;

status = "okay";

interrupt-parent = <0x1>;

};

sysbusclock@0 {

#clock-cells = <0x0>;

compatible = "mtk,mt7621-sys-bus-clock";

phandle = <0x5>;

linux,phandle = <0x5>;

};

cpuclock@0 {

#clock-cells = <0x0>;

compatible = "mtk,mt7621-cpu-clock";

phandle = <0x14>;

linux,phandle = <0x14>;

};

cpuintc@0 {

compatible = "mti,cpu-interrupt-controller";

#interrupt-cells = <0x1>;

#address-cells = <0x0>;

interrupt-controller;

};

clkctrl {

#clock-cells = <0x1>;

compatible = "ralink,rt2880-clock";

phandle = <0xe>;

linux,phandle = <0xe>;

};

};

I will receive a BELKIN RT1800

is this the device that the firmware work on tenbay?

???

this means that the wan port is port4, but the openwrt dts say that tenbay wan is port0

i'm really confuse now

The zbr-z100 ax firmware is also 4.4.198 & run with the tenbay ( only no leds functionality )

this is the firmware that I put in the tenbay

if I manage to compile in nor version I hope that it will be possible to see for the leds

I will also see to make the files with an SPI of 32M

mediatek,portmap = "llllw"; is the schematic for lan / wan ports -> l is for LNA ports , w for WAN port

if ports are not in good physical order you can use wllll

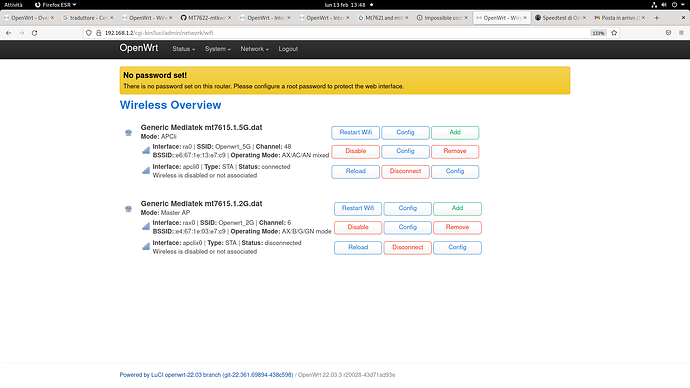

root@OpenWrt:~# iwconfig

lo no wireless extensions.

eth0 no wireless extensions.

wan no wireless extensions.

lan1 no wireless extensions.

lan2 no wireless extensions.

lan3 no wireless extensions.

lan4 no wireless extensions.

rax0 RTWIFI SoftAP ESSID:"CR660X_2.4G"

Mode:Master Channel=6 Access Point: E4:67:1E:03:E7:C9

Bit Rate=541 Mb/s

Link Quality:10 Signal level:0 Noise level:0

Rx invalid nwid:0 invalid crypt:0 invalid misc:0

br-lan no wireless extensions.

ra0 RTWIFI SoftAP ESSID:"Openwrt_5G"

Mode:Master Channel=44 Access Point: E6:67:1E:13:E7:C9

Bit Rate=1.134 Gb/s

Link Quality:10 Signal level:0 Noise level:0

Rx invalid nwid:0 invalid crypt:0 invalid misc:0

apclix0 RTWIFI SoftAP ESSID:""

Mode:Managed Channel=6 Access Point: Not-Associated

Bit Rate:541 Mb/s

Link Quality:10 Signal level:0 Noise level:0

Rx invalid nwid:0 invalid crypt:0 invalid misc:0

apcli0 RTWIFI SoftAP ESSID:""

Mode:Managed Channel=44 Access Point: Not-Associated

Bit Rate:1.134 Gb/s

Link Quality:10 Signal level:0 Noise level:0

Rx invalid nwid:0 invalid crypt:0 invalid misc:0

root@OpenWrt:~#

well i don't know if i need close this, but anyway i ll not to publish the code, because i do not want other fake OPENWRT use that.

@anon4457646 - I find it a bit confusing that you have gone to the effort of improving drivers for OpenWrt, but will not publish it for the greater community.

I'm not sure why you have such a 'close-hold' approach to this. First of all, what about the official OpenWrt (which is an open source project)? The aim of OpenWrt is to provide a free and freely available firmware that is more powerful, performant (when possible with FOSS code), flexible and up-to-date than most vendor firmware releases. Yes, there are forks and deriviative firmware versions that are not official, but the world still benefits from the contributions of OpenWrt developers.

That said, if you do not want to release your code, that is your right. However, it seems to be a wasted opportunity. And if you are not planning to release your code, we will go ahead and close this thread since it no longer has general appplicability to OpenWrt.

when I say there are problems with MT76 drivers or with OpenWrt as I have been doing for some time...

for me two problems that do not exist with OEM firmware OpenWrt 17.01

it is impossible to operate in sta / ap mode with the wifi6 of my Livebox 6 Orange

exist with all MT7621 OpenWrt firmware

exist also with AsRock G10 ( not MT7621 )

the speed of WIFI AX/6 is much better than with OpenWrt drivers

what do you recommend other than: if it does not suit you use the OEM firmware which I have already read many times?

where are the bug reports?

Can you please explain a bit more what you mean by "other fake OPENWRT"?

Sorry I did not even see this thread until today! I wish I had as I could have helped with testing. I have a 7621 USB wireless device. I have been running this about a year I think, and have not experienced major problems with it.

Occasionally I see one of those situations where the openwrt console goes nuts with error messages from the device, but I also see this with other USB devices at seemingly random times. But, again, the standard issue driver (e.g., openwrt 22.03.3's 7621 drivers) is very stable overall. I have not tried your version.

I agree with others here--you should release the code. Who cares if other projects or individuals "steal" the code? We can steal theirs too (if open sourced).

vendors, or people that clone openwrt repo

today is guglielmo marconi day in italy. openwrt padre.

so buon onomastico MARCONI

What is your objection to others using the code you have developed/improved?

nothing, just alot work, and i'll share that only with openwrt

i do not want say why, also i said.

they use openrwt to sell devices.

i use openwrt because i love it.