With Ghira help I write down a small utility to extract from rtkcore.ko - what I think - are the correct port definition that actually match what is observed from the bootlog. The various hwp structures are the same in the u-boot binary so I assume this should be corrcet.

I am quite sure the serdes are starting at 2 both on the 8 and 5 ports version, but I am unable to make the ethernet work. I am quite sure - with the same dts - I was able to make it work.

Here what I have extracted from the binary

:Hasivo 5 ports

Searching for [RTL9303_5X8226] in [../rtcore.ko]

Looking for pattern [x00x00x00x00x52x54x4cx39x33x30x33x5fx35x58x38x32x32x36x00]...found at 0x670a4

Profile name: RTL9303_5X8226

Switch chip id : 0x93036810

Core supported : 0x1

Core access : 0x0

Nic supported : 0x0

Switch ports descrption:

.mac_id = 0, .phyIdx=0 smi=0 phy_addr=1 sds_idx=0

.mac_id = 8, .phyIdx=1 smi=0 phy_addr=2 sds_idx=1

.mac_id = 16, .phyIdx=2 smi=0 phy_addr=3 sds_idx=2

.mac_id = 20, .phyIdx=3 smi=0 phy_addr=4 sds_idx=3

.mac_id = 24, .phyIdx=4 smi=1 phy_addr=1 sds_idx=4

.mac_id = 25, .phyIdx=255 smi=255 phy_addr=255 sds_idx=5

.mac_id = 26, .phyIdx=255 smi=255 phy_addr=255 sds_idx=6

.mac_id = 27, .phyIdx=255 smi=255 phy_addr=255 sds_idx=7

.mac_id = 28, .phyIdx=255 smi=255 phy_addr=255 sds_idx=255

Serdes descrption:

.sds_idx=2, .mode=28, .rx_polarity=1, .tx_polarity=0

.sds_idx=3, .mode=28, .rx_polarity=1, .tx_polarity=0

.sds_idx=4, .mode=28, .rx_polarity=1, .tx_polarity=0

.sds_idx=5, .mode=28, .rx_polarity=1, .tx_polarity=0

.sds_idx=6, .mode=28, .rx_polarity=1, .tx_polarity=0

.sds_idx=7, .mode=28, .rx_polarity=1, .tx_polarity=0

.sds_idx=8, .mode=8, .rx_polarity=0, .tx_polarity=0

.sds_idx=9, .mode=8, .rx_polarity=0, .tx_polarity=0

Phy descrption:

.chip=19, .phy_max=1, .mac_id=0

.chip=19, .phy_max=1, .mac_id=8

.chip=19, .phy_max=1, .mac_id=16

.chip=19, .phy_max=1, .mac_id=20

.chip=19, .phy_max=1, .mac_id=24

::Hasivo 8 ports

Searching for [RTL9303_8X8226] in [../rtcore.ko]

Looking for pattern [x00x00x00x00x52x54x4cx39x33x30x33x5fx38x58x38x32x32x36x00]...found at 0x67e24

Profile name: RTL9303_8X8226

Switch chip id : 0x93036810

Core supported : 0x1

Core access : 0x0

Nic supported : 0x0

Switch ports descrption:

.mac_id = 0, .phyIdx=0 smi=0 phy_addr=1 sds_idx=0

.mac_id = 8, .phyIdx=1 smi=0 phy_addr=2 sds_idx=1

.mac_id = 16, .phyIdx=2 smi=0 phy_addr=3 sds_idx=2

.mac_id = 20, .phyIdx=3 smi=0 phy_addr=4 sds_idx=3

.mac_id = 24, .phyIdx=4 smi=1 phy_addr=1 sds_idx=4

.mac_id = 25, .phyIdx=5 smi=1 phy_addr=2 sds_idx=5

.mac_id = 26, .phyIdx=6 smi=1 phy_addr=3 sds_idx=6

.mac_id = 27, .phyIdx=7 smi=1 phy_addr=4 sds_idx=7

.mac_id = 28, .phyIdx=255 smi=255 phy_addr=255 sds_idx=255

Serdes descrption:

.sds_idx=2, .mode=28, .rx_polarity=1, .tx_polarity=0

.sds_idx=3, .mode=28, .rx_polarity=1, .tx_polarity=0

.sds_idx=4, .mode=28, .rx_polarity=1, .tx_polarity=0

.sds_idx=5, .mode=28, .rx_polarity=1, .tx_polarity=0

.sds_idx=6, .mode=28, .rx_polarity=1, .tx_polarity=0

.sds_idx=7, .mode=28, .rx_polarity=1, .tx_polarity=0

.sds_idx=8, .mode=28, .rx_polarity=1, .tx_polarity=0

.sds_idx=9, .mode=28, .rx_polarity=1, .tx_polarity=0

Phy descrption:

.chip=19, .phy_max=1, .mac_id=0

.chip=19, .phy_max=1, .mac_id=8

.chip=19, .phy_max=1, .mac_id=16

.chip=19, .phy_max=1, .mac_id=20

.chip=19, .phy_max=1, .mac_id=24

.chip=19, .phy_max=1, .mac_id=25

.chip=19, .phy_max=1, .mac_id=26

.chip=19, .phy_max=1, .mac_id=27

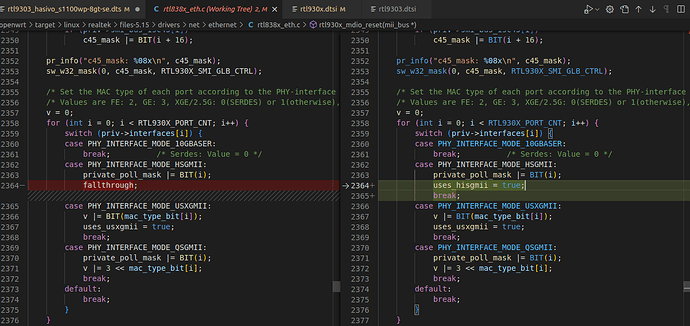

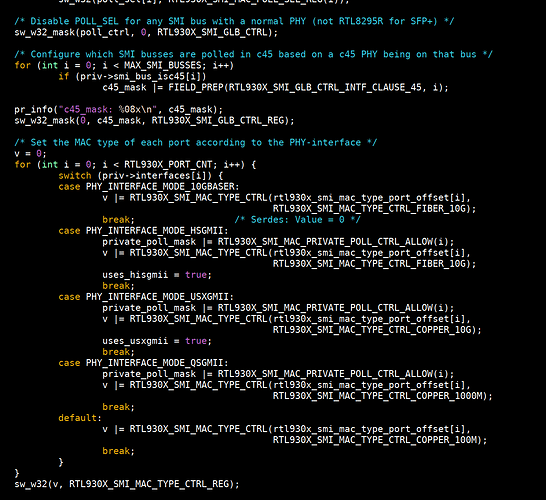

And here the relevant dts section I am using. Please note the smi-address I matched to what we see in the bin starting with <0 1> uop to <0 4> and then <1 1>. I am also trying to use the mac_ids aas port numbers but I am under the impression there is no initialization (if I bypass the the rtk network on in u-boot). Any ideas?

ðernet0 {

mdio: mdio-bus {

compatible = "realtek,rtl9303-mdio", "realtek,rtl930x-mdio", "realtek,rtl838x-mdio";

regmap = <ðernet0>;

#address-cells = <1>;

#size-cells = <0>;

/* External RTL8226 2.5G phy */

phy0: ethernet-phy@0 {

reg = <0>;

compatible = "ethernet-phy-ieee802.3-c45";

rtl9300,smi-address = <0 1>;

sds = < 2 >;

//max-speed = <2500>;

};

phy8: ethernet-phy@8 {

reg = <8>;

compatible = "ethernet-phy-ieee802.3-c45";

rtl9300,smi-address = <0 2>;

sds = < 3 >;

//max-speed = <2500>;

};

phy16: ethernet-phy@16 {

reg = <16>;

compatible = "ethernet-phy-ieee802.3-c45";

rtl9300,smi-address = <0 3>;

sds = < 4 >;

//max-speed = <2500>;

};

phy20: ethernet-phy@20 {

reg = <20>;

compatible = "ethernet-phy-ieee802.3-c45";

rtl9300,smi-address = <0 4>;

sds = < 5 >;

//max-speed = <2500>;

};

phy24: ethernet-phy@24 {

reg = <24>;

compatible = "ethernet-phy-ieee802.3-c45";

rtl9300,smi-address = <1 1>;

sds = < 6 >;

//max-speed = <2500>;

};

};

};

witch0_ports {

port@0 {

reg = <0>;

label = "lan1";

led-num = <(

RTL93XX_LED_NUM0 | /* Orange */

RTL93XX_LED_NUM1 | /* Lime */

RTL93XX_LED_NUM2 /* Lime */

)>;

led-set = <0>;

phy-mode = "hsgmii";

phy-handle = <&phy0>;

};

port@8 {

reg = <8>;

label = "lan2";

led-num = <(

RTL93XX_LED_NUM0 | /* Orange */

RTL93XX_LED_NUM1 | /* Lime */

RTL93XX_LED_NUM2 /* Lime */

)>;

led-set = <0>;

phy-mode = "hsgmii";

phy-handle = <&phy8>;

};

port@16 {

reg = <16>;

label = "lan3";

led-num = <(

RTL93XX_LED_NUM0 | /* Orange */

RTL93XX_LED_NUM1 | /* Lime */

RTL93XX_LED_NUM2 /* Lime */

)>;

led-set = <0>;

phy-mode = "hsgmii";

phy-handle = <&phy16>;

};

port@20 {

reg = <20>;

label = "lan4";

led-num = <(

RTL93XX_LED_NUM0 | /* Orange */

RTL93XX_LED_NUM1 | /* Lime */

RTL93XX_LED_NUM2 /* Lime */

)>;

led-set = <0>;

phy-mode = "hsgmii";

phy-handle = <&phy20>;

};

port@24 {

reg = <24>;

label = "lan5";

led-num = <(

RTL93XX_LED_NUM0 | /* Orange */

RTL93XX_LED_NUM1 | /* Lime */

RTL93XX_LED_NUM2 /* Lime */

)>;

led-set = <0>;

phy-mode = "hsgmii";

phy-handle = <&phy24>;

};

};