Hi,

@Dairyman from the ROOTer Team has initially added support for this router, unfortunately there is a problem with the hardware watchdog which restarts the router every 1/2 minute. I'm starting this topic with the thought that maybe someone has had a similar problem before and can tell us how to solve it.

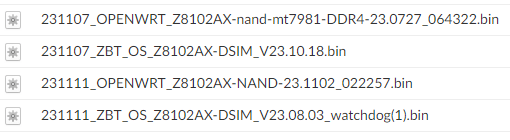

ZBT OpenWrt fork

cat /sys/kernel/debug/gpio

gpiochip0: GPIOs 455-511, parent: platform/11d00000.pinctrl, pinctrl_moore:

gpio-455 ( |mesh ) in hi IRQ

gpio-456 ( |reset ) in hi IRQ ACTIVE LOW

gpio-457 ( |wdg ) out lo

gpio-458 ( |pcie ) out hi

gpio-459 ( |4g ) out hi

gpio-460 ( |4g2 ) out hi

gpio-461 ( |sim1 ) out lo

gpio-462 ( |sim2 ) out lo

gpio-463 ( |4g ) out hi ACTIVE LOW

gpio-464 ( |red ) out hi

gpio-465 ( |green ) out lo ACTIVE LOW

gpio-466 ( |blue ) out hi ACTIVE LOW

gpio-467 ( |hub ) in lo IRQ

gpio-468 ( |4g2 ) out hi ACTIVE LOW

gpio-494 ( |reset ) out hi

our OpenWrt

cat /sys/kernel/debug/gpio

gpiochip0: GPIOs 455-511, parent: platform/11d00000.pinctrl, pinctrl_moore:

gpio-455 ( |wps ) in hi IRQ ACTIVE LOW

gpio-456 ( |reset ) in hi IRQ ACTIVE LOW

gpio-459 ( |sysfs ) out hi

gpio-460 ( |sysfs ) out hi

gpio-461 ( |sysfs ) out lo

gpio-462 ( |sysfs ) out lo

gpio-463 ( |4g:status ) out hi ACTIVE LOW

gpio-464 ( |red:status ) out hi ACTIVE LOW

gpio-465 ( |green:status ) out lo ACTIVE LOW

gpio-466 ( |blue:status ) out hi ACTIVE LOW

gpio-467 ( |regulator-usb-vbus ) out hi

gpio-468 ( |4g2:status ) out hi ACTIVE LOW

gpio-494 ( |reset ) out hi

ROOTer Team zbt-z8102ax.dts

ZBT OpenWrt fork (dts extracted from the image)

/dts-v1/;

/ {

compatible = "mediatek,mt7981-spim-snand-rfb-z8102ax";

interrupt-parent = <0x01>;

#address-cells = <0x02>;

#size-cells = <0x02>;

model = "MediaTek MT7981 RFB";

cpus {

#address-cells = <0x01>;

#size-cells = <0x00>;

cpu@0 {

device_type = "cpu";

compatible = "arm,cortex-a53";

enable-method = "psci";

reg = <0x00>;

};

cpu@1 {

device_type = "cpu";

compatible = "arm,cortex-a53";

enable-method = "psci";

reg = <0x01>;

};

};

pwm@10048000 {

compatible = "mediatek,mt7981-pwm";

reg = <0x00 0x10048000 0x00 0x1000>;

#pwm-cells = <0x02>;

clocks = <0x02 0x0d 0x02 0x0c 0x02 0x0e 0x02 0x0f 0x02 0x10>;

clock-names = "top\0main\0pwm1\0pwm2\0pwm3";

};

thermal-zones {

cpu-thermal {

polling-delay-passive = <0x3e8>;

polling-delay = <0x3e8>;

thermal-sensors = <0x03 0x00>;

};

};

thermal@1100c800 {

#thermal-sensor-cells = <0x01>;

compatible = "mediatek,mt7981-thermal";

reg = <0x00 0x1100c800 0x00 0x800>;

interrupts = <0x00 0x8a 0x04>;

clocks = <0x02 0x1c 0x02 0x2f 0x02 0x30>;

clock-names = "therm\0auxadc\0adc_32k";

mediatek,auxadc = <0x04>;

mediatek,apmixedsys = <0x05>;

nvmem-cells = <0x06>;

nvmem-cell-names = "calibration-data";

phandle = <0x03>;

};

adc@1100d000 {

compatible = "mediatek,mt7981-auxadc\0mediatek,mt7622-auxadc";

reg = <0x00 0x1100d000 0x00 0x1000>;

clocks = <0x02 0x2f 0x02 0x30>;

clock-names = "main\032k";

#io-channel-cells = <0x01>;

phandle = <0x04>;

};

wed@15010000 {

compatible = "mediatek,wed";

wed_num = <0x02>;

pci_slot_map = <0x00 0x01>;

reg = <0x00 0x15010000 0x00 0x1000 0x00 0x15011000 0x00 0x1000>;

interrupt-parent = <0x01>;

interrupts = <0x00 0xcd 0x04 0x00 0xce 0x04>;

};

wdma@15104800 {

compatible = "mediatek,wed-wdma";

reg = <0x00 0x15104800 0x00 0x400 0x00 0x15104c00 0x00 0x400>;

};

ap2woccif@151A5000 {

compatible = "mediatek,ap2woccif";

reg = <0x00 0x151a5000 0x00 0x1000 0x00 0x151ad000 0x00 0x1000>;

interrupt-parent = <0x01>;

interrupts = <0x00 0xd3 0x04 0x00 0xd4 0x04>;

};

wocpu0_ilm@151E0000 {

compatible = "mediatek,wocpu0_ilm";

reg = <0x00 0x151e0000 0x00 0x8000>;

};

wocpu_dlm@151E8000 {

compatible = "mediatek,wocpu_dlm";

reg = <0x00 0x151e8000 0x00 0x2000 0x00 0x151f8000 0x00 0x2000>;

resets = <0x07 0x00>;

reset-names = "wocpu_rst";

};

wocpu_boot@15194000 {

compatible = "mediatek,wocpu_boot";

reg = <0x00 0x15194000 0x00 0x1000>;

};

reserved-memory {

#address-cells = <0x02>;

#size-cells = <0x02>;

ranges;

secmon@43000000 {

reg = <0x00 0x43000000 0x00 0x30000>;

no-map;

};

wmcpu-reserved@47C80000 {

compatible = "mediatek,wmcpu-reserved";

no-map;

reg = <0x00 0x47c80000 0x00 0x100000>;

phandle = <0x17>;

};

wocpu0_emi@47D80000 {

compatible = "mediatek,wocpu0_emi";

no-map;

reg = <0x00 0x47d80000 0x00 0x40000>;

shared = <0x00>;

};

wocpu_data@47DC0000 {

compatible = "mediatek,wocpu_data";

no-map;

reg = <0x00 0x47dc0000 0x00 0x240000>;

shared = <0x01>;

};

};

psci {

compatible = "arm,psci-0.2";

method = "smc";

};

oscillator@0 {

compatible = "fixed-clock";

#clock-cells = <0x00>;

clock-frequency = <0x2625a00>;

clock-output-names = "clkxtal";

phandle = <0x1d>;

};

infracfg_ao@10001000 {

compatible = "mediatek,mt7981-infracfg_ao\0syscon";

reg = <0x00 0x10001000 0x00 0x68>;

#clock-cells = <0x01>;

phandle = <0x02>;

};

infracfg@10001040 {

compatible = "mediatek,mt7981-infracfg\0syscon";

reg = <0x00 0x10001068 0x00 0x1000>;

#clock-cells = <0x01>;

phandle = <0x09>;

};

topckgen@1001B000 {

compatible = "mediatek,mt7981-topckgen\0syscon";

reg = <0x00 0x1001b000 0x00 0x1000>;

#clock-cells = <0x01>;

phandle = <0x08>;

};

apmixedsys@1001E000 {

compatible = "mediatek,mt7981-apmixedsys\0syscon";

reg = <0x00 0x1001e000 0x00 0x1000>;

#clock-cells = <0x01>;

phandle = <0x05>;

};

dummy_system_clk {

compatible = "fixed-clock";

clock-frequency = <0x2625a00>;

#clock-cells = <0x00>;

phandle = <0x19>;

};

dummy_gpt_clk {

compatible = "fixed-clock";

clock-frequency = <0x1312d00>;

#clock-cells = <0x00>;

};

timer {

compatible = "arm,armv8-timer";

interrupt-parent = <0x01>;

clock-frequency = <0xc65d40>;

interrupts = <0x01 0x0d 0x08 0x01 0x0e 0x08 0x01 0x0b 0x08 0x01 0x0a 0x08>;

};

watchdog@1001c000 {

compatible = "mediatek,mt7622-wdt\0mediatek,mt6589-wdt";

reg = <0x00 0x1001c000 0x00 0x1000>;

interrupts = <0x00 0x6e 0x04>;

#reset-cells = <0x01>;

status = "okay";

};

interrupt-controller@c000000 {

compatible = "arm,gic-v3";

#interrupt-cells = <0x03>;

interrupt-parent = <0x01>;

interrupt-controller;

reg = <0x00 0xc000000 0x00 0x40000 0x00 0xc080000 0x00 0x200000>;

interrupts = <0x01 0x09 0x04>;

phandle = <0x01>;

};

trng@1020f000 {

compatible = "mediatek,mt7981-rng";

};

serial@11002000 {

compatible = "mediatek,mt6577-uart";

reg = <0x00 0x11002000 0x00 0x400>;

interrupts = <0x00 0x7b 0x04>;

clocks = <0x02 0x1e>;

assigned-clocks = <0x08 0x50 0x02 0x00>;

assigned-clock-parents = <0x08 0x00 0x09 0x01>;

status = "okay";

};

serial@11003000 {

compatible = "mediatek,mt6577-uart";

reg = <0x00 0x11003000 0x00 0x400>;

interrupts = <0x00 0x7c 0x04>;

clocks = <0x02 0x1f>;

assigned-clocks = <0x08 0x50 0x02 0x01>;

assigned-clock-parents = <0x08 0x00 0x09 0x01>;

status = "disabled";

};

serial@11004000 {

compatible = "mediatek,mt6577-uart";

reg = <0x00 0x11004000 0x00 0x400>;

interrupts = <0x00 0x7d 0x04>;

clocks = <0x02 0x20>;

assigned-clocks = <0x08 0x50 0x02 0x02>;

assigned-clock-parents = <0x08 0x00 0x09 0x01>;

status = "disabled";

};

i2c@11007000 {

compatible = "mediatek,mt7981-i2c";

reg = <0x00 0x11007000 0x00 0x1000 0x00 0x10217080 0x00 0x80>;

interrupts = <0x00 0x88 0x04>;

clock-div = <0x01>;

clocks = <0x02 0x1d 0x02 0x19>;

clock-names = "main\0dma";

#address-cells = <0x01>;

#size-cells = <0x00>;

status = "disabled";

pinctrl-names = "default";

pinctrl-0 = <0x0a>;

wm8960@1a {

compatible = "wlf,wm8960";

reg = <0x1a>;

phandle = <0x21>;

};

};

pcie@11280000 {

compatible = "mediatek,mt7981-pcie\0mediatek,mt7986-pcie";

device_type = "pci";

reg = <0x00 0x11280000 0x00 0x4000>;

reg-names = "pcie-mac";

#address-cells = <0x03>;

#size-cells = <0x02>;

interrupts = <0x00 0xa8 0x04>;

bus-range = <0x00 0xff>;

ranges = <0x82000000 0x00 0x20000000 0x00 0x20000000 0x00 0x10000000>;

status = "disabled";

clocks = <0x02 0x38 0x02 0x39 0x02 0x3a 0x02 0x3b>;

phys = <0x0b 0x02>;

phy-names = "pcie-phy";

#interrupt-cells = <0x01>;

interrupt-map-mask = <0x00 0x00 0x00 0x07>;

interrupt-map = <0x00 0x00 0x00 0x01 0x0c 0x00 0x00 0x00 0x00 0x02 0x0c 0x01 0x00 0x00 0x00 0x03 0x0c 0x02 0x00 0x00 0x00 0x04 0x0c 0x03>;

interrupt-controller {

interrupt-controller;

#address-cells = <0x00>;

#interrupt-cells = <0x01>;

phandle = <0x0c>;

};

};

crypto@10320000 {

compatible = "inside-secure,safexcel-eip97";

reg = <0x00 0x10320000 0x00 0x40000>;

interrupts = <0x00 0x74 0x04 0x00 0x75 0x04 0x00 0x76 0x04 0x00 0x77 0x04>;

interrupt-names = "ring0\0ring1\0ring2\0ring3";

clocks = <0x08 0x42>;

clock-names = "top_eip97_ck";

assigned-clocks = <0x08 0x63>;

assigned-clock-parents = <0x08 0x15>;

};

pinctrl@11d00000 {

compatible = "mediatek,mt7981-pinctrl";

reg = <0x00 0x11d00000 0x00 0x1000 0x00 0x11c00000 0x00 0x1000 0x00 0x11c10000 0x00 0x1000 0x00 0x11d20000 0x00 0x1000 0x00 0x11e00000 0x00 0x1000 0x00 0x11e20000 0x00 0x1000 0x00 0x11f00000 0x00 0x1000 0x00 0x11f10000 0x00 0x1000 0x00 0x1000b000 0x00 0x1000>;

reg-names = "gpio_base\0iocfg_rt_base\0iocfg_rm_base\0iocfg_rb_base\0iocfg_lb_base\0iocfg_bl_base\0iocfg_tm_base\0iocfg_tl_base\0eint";

gpio-controller;

#gpio-cells = <0x02>;

gpio-ranges = <0x0d 0x00 0x00 0x38>;

interrupt-controller;

interrupts = <0x00 0xe1 0x04>;

interrupt-parent = <0x01>;

#interrupt-cells = <0x02>;

phandle = <0x0d>;

i2c-pins-g0 {

phandle = <0x0a>;

mux {

function = "i2c";

groups = "i2c0_0";

};

};

pcm-pins-g0 {

phandle = <0x1e>;

mux {

function = "pcm";

groups = "pcm";

};

};

pwm0-pin-g0 {

mux {

function = "pwm";

groups = "pwm0_0";

};

};

pwm1-pin-g0 {

mux {

function = "pwm";

groups = "pwm1_0";

};

};

pwm2-pin {

mux {

function = "pwm";

groups = "pwm2";

};

};

spi0-pins {

phandle = <0x15>;

mux {

function = "spi";

groups = "spi0\0spi0_wp_hold";

};

conf-pu {

pins = "SPI0_CS\0SPI0_HOLD\0SPI0_WP";

drive-strength = <0x08>;

bias-pull-up = <0x67>;

};

conf-pd {

pins = "SPI0_CLK\0SPI0_MOSI\0SPI0_MISO";

drive-strength = <0x08>;

bias-pull-down = <0x67>;

};

};

spi1-pins {

phandle = <0x16>;

mux {

function = "spi";

groups = "spi1_1";

};

};

uart1-pins-g1 {

mux {

function = "uart";

groups = "uart1_1";

};

};

uart2-pins-g1 {

mux {

function = "uart";

groups = "uart2_1";

};

};

};

syscon@15000000 {

#address-cells = <0x01>;

#size-cells = <0x01>;

compatible = "mediatek,mt7981-ethsys\0syscon";

reg = <0x00 0x15000000 0x00 0x1000>;

#clock-cells = <0x01>;

#reset-cells = <0x01>;

phandle = <0x0e>;

reset-controller {

compatible = "ti,syscon-reset";

#reset-cells = <0x01>;

ti,reset-bits = <0x34 0x04 0x34 0x04 0x34 0x04 0x28>;

phandle = <0x07>;

};

};

ethernet@15100000 {

compatible = "mediatek,mt7981-eth";

reg = <0x00 0x15100000 0x00 0x80000>;

interrupts = <0x00 0xc4 0x04 0x00 0xc5 0x04 0x00 0xc6 0x04 0x00 0xc7 0x04>;

clocks = <0x0e 0x00 0x0e 0x01 0x0e 0x02 0x0e 0x03 0x0f 0x00 0x0f 0x01 0x0f 0x02 0x0f 0x03 0x10 0x00 0x10 0x01 0x10 0x02 0x10 0x03>;

clock-names = "fe\0gp2\0gp1\0wocpu0\0sgmii_tx250m\0sgmii_rx250m\0sgmii_cdr_ref\0sgmii_cdr_fb\0sgmii2_tx250m\0sgmii2_rx250m\0sgmii2_cdr_ref\0sgmii2_cdr_fb";

assigned-clocks = <0x08 0x60 0x08 0x61>;

assigned-clock-parents = <0x08 0x1b 0x08 0x22>;

mediatek,ethsys = <0x0e>;

mediatek,sgmiisys = <0x0f 0x10>;

mediatek,infracfg = <0x11>;

#reset-cells = <0x01>;

#address-cells = <0x01>;

#size-cells = <0x00>;

status = "okay";

mac@0 {

compatible = "mediatek,eth-mac";

reg = <0x00>;

phy-mode = "2500base-x";

phandle = <0x14>;

fixed-link {

speed = <0x9c4>;

full-duplex;

pause;

};

};

mac@1 {

compatible = "mediatek,eth-mac";

reg = <0x01>;

phy-mode = "gmii";

phy-handle = <0x12>;

};

mdio-bus {

#address-cells = <0x01>;

#size-cells = <0x00>;

ethernet-phy@0 {

compatible = "ethernet-phy-id03a2.9461";

reg = <0x00>;

phy-mode = "gmii";

nvmem-cells = <0x13>;

nvmem-cell-names = "phy-cal-data";

phandle = <0x12>;

};

switch@0 {

compatible = "mediatek,mt7531";

reg = <0x1f>;

reset-gpios = <0x0d 0x27 0x00>;

ports {

#address-cells = <0x01>;

#size-cells = <0x00>;

port@0 {

reg = <0x00>;

label = "lan1";

};

port@1 {

reg = <0x01>;

label = "lan2";

};

port@2 {

reg = <0x02>;

label = "lan3";

};

port@3 {

reg = <0x03>;

label = "lan4";

};

port@6 {

reg = <0x06>;

label = "cpu";

ethernet = <0x14>;

phy-mode = "2500base-x";

fixed-link {

speed = <0x9c4>;

full-duplex;

pause;

};

};

};

};

};

};

hnat@15000000 {

compatible = "mediatek,mtk-hnat_v4";

reg = <0x00 0x15100000 0x00 0x80000>;

resets = <0x0e 0x00>;

reset-names = "mtketh";

status = "okay";

mtketh-wan = "eth1";

mtketh-lan = "lan";

mtketh-max-gmac = <0x02>;

};

syscon@10060000 {

compatible = "mediatek,mt7981-sgmiisys_0\0syscon";

reg = <0x00 0x10060000 0x00 0x1000>;

pn_swap;

#clock-cells = <0x01>;

phandle = <0x0f>;

};

syscon@10070000 {

compatible = "mediatek,mt7981-sgmiisys_1\0syscon";

reg = <0x00 0x10070000 0x00 0x1000>;

#clock-cells = <0x01>;

phandle = <0x10>;

};

topmisc@11d10000 {

compatible = "mediatek,mt7981-topmisc\0syscon";

reg = <0x00 0x11d10000 0x00 0x10000>;

#clock-cells = <0x01>;

phandle = <0x11>;

};

snfi@11005000 {

compatible = "mediatek,mt7986-snand";

reg = <0x00 0x11005000 0x00 0x1000 0x00 0x11006000 0x00 0x1000>;

reg-names = "nfi\0ecc";

interrupts = <0x00 0x79 0x04>;

clocks = <0x02 0x24 0x02 0x23 0x02 0x25>;

clock-names = "pad_clk\0nfi_clk\0nfi_hclk";

assigned-clocks = <0x08 0x4d 0x08 0x4c>;

assigned-clock-parents = <0x08 0x06 0x08 0x06>;

#address-cells = <0x01>;

#size-cells = <0x00>;

status = "disabled";

};

mmc@11230000 {

compatible = "mediatek,mt7986-mmc\0mediatek,mt7981-mmc";

reg = <0x00 0x11230000 0x00 0x1000 0x00 0x11c20000 0x00 0x1000>;

interrupts = <0x00 0x8f 0x04>;

clocks = <0x08 0x33 0x08 0x34 0x02 0x2b>;

assigned-clocks = <0x08 0x54 0x08 0x55>;

assigned-clock-parents = <0x08 0x02 0x08 0x1c>;

clock-names = "source\0hclk\0source_cg";

status = "disabled";

};

wbsys@18000000 {

compatible = "mediatek,wbsys";

reg = <0x00 0x18000000 0x00 0x1000000>;

interrupts = <0x00 0xd5 0x04 0x00 0xd6 0x04 0x00 0xd7 0x04 0x00 0xd8 0x04>;

chip_id = <0x7981>;

};

wed_pcie@10003000 {

compatible = "mediatek,wed_pcie";

reg = <0x00 0x10003000 0x00 0x10>;

};

spi@1100a000 {

compatible = "mediatek,ipm-spi-quad";

reg = <0x00 0x1100a000 0x00 0x100>;

interrupts = <0x00 0x8c 0x04>;

clocks = <0x08 0x02 0x08 0x4e 0x02 0x26 0x02 0x28>;

clock-names = "parent-clk\0sel-clk\0spi-clk\0spi-hclk";

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <0x15>;

spi_nand@0 {

#address-cells = <0x01>;

#size-cells = <0x01>;

compatible = "spi-nand";

reg = <0x00>;

spi-max-frequency = <0x3197500>;

spi-tx-buswidth = <0x04>;

spi-rx-buswidth = <0x04>;

phandle = <0x1f>;

};

};

spi@1100b000 {

compatible = "mediatek,ipm-spi-single";

reg = <0x00 0x1100b000 0x00 0x100>;

interrupts = <0x00 0x8d 0x04>;

clocks = <0x08 0x02 0x08 0x4f 0x02 0x27 0x02 0x29>;

clock-names = "parent-clk\0sel-clk\0spi-clk\0spi-hclk";

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <0x16>;

proslic_spi@0 {

compatible = "silabs,proslic_spi";

reg = <0x00>;

spi-max-frequency = <0x989680>;

spi-cpha = <0x01>;

spi-cpol = <0x01>;

channel_count = <0x01>;

debug_level = <0x04>;

reset_gpio = <0x0d 0x0f 0x00>;

ig,enable-spi = <0x01>;

phandle = <0x22>;

};

};

spi@11009000 {

compatible = "mediatek,ipm-spi-quad";

reg = <0x00 0x11009000 0x00 0x100>;

interrupts = <0x00 0x8e 0x04>;

clocks = <0x08 0x02 0x08 0x4e 0x02 0x21 0x02 0x22>;

clock-names = "parent-clk\0sel-clk\0spi-clk\0spi-hclk";

status = "disabled";

};

consys@10000000 {

compatible = "mediatek,mt7981-consys";

reg = <0x00 0x10000000 0x00 0x8600000>;

memory-region = <0x17>;

};

xhci@11200000 {

compatible = "mediatek,mt7986-xhci\0mediatek,mtk-xhci";

reg = <0x00 0x11200000 0x00 0x2e00 0x00 0x11203e00 0x00 0x100>;

reg-names = "mac\0ippc";

interrupts = <0x00 0xad 0x04>;

phys = <0x18 0x03 0x0b 0x04>;

clocks = <0x19 0x19 0x19 0x19 0x19>;

clock-names = "sys_ck\0xhci_ck\0ref_ck\0mcu_ck\0dma_ck";

#address-cells = <0x02>;

#size-cells = <0x02>;

mediatek,u3p-dis-msk = <0x00>;

status = "okay";

};

usb-phy@11e10000 {

compatible = "mediatek,mt7986\0mediatek,generic-tphy-v2";

#address-cells = <0x02>;

#size-cells = <0x02>;

ranges;

status = "okay";

usb-phy@11e10000 {

reg = <0x00 0x11e10000 0x00 0x700>;

clocks = <0x19>;

clock-names = "ref";

#phy-cells = <0x01>;

status = "okay";

phandle = <0x18>;

};

usb-phy@11e10700 {

reg = <0x00 0x11e10700 0x00 0x900>;

clocks = <0x19>;

clock-names = "ref";

#phy-cells = <0x01>;

mediatek,syscon-type = <0x11 0x218 0x00>;

nvmem-cells = <0x1a 0x1b 0x1c>;

nvmem-cell-names = "intr\0rx_imp\0tx_imp";

status = "okay";

phandle = <0x0b>;

};

};

regulator-3p3v {

compatible = "regulator-fixed";

regulator-name = "fixed-3.3V";

regulator-min-microvolt = <0x325aa0>;

regulator-max-microvolt = <0x325aa0>;

regulator-boot-on;

regulator-always-on;

};

clkitg {

compatible = "simple-bus";

bring-up {

compatible = "mediatek,clk-bring-up";

clocks = <0x05 0x00 0x05 0x01 0x05 0x02 0x05 0x03 0x05 0x04 0x05 0x05 0x05 0x06 0x05 0x07 0x09 0x00 0x1d 0x09 0x02 0x09 0x03 0x09 0x04 0x1d 0x09 0x06 0x09 0x07 0x1d 0x1d 0x1d 0x1d 0x09 0x0c 0x09 0x0d 0x09 0x0e 0x09 0x0f 0x09 0x10 0x09 0x11 0x1d 0x1d 0x1d 0x1d 0x1d 0x09 0x17 0x09 0x18 0x09 0x1a 0x09 0x1b 0x09 0x1c 0x09 0x1d 0x09 0x1e 0x09 0x1f 0x09 0x20 0x09 0x21 0x1d 0x09 0x23 0x1d 0x1d 0x1d 0x1d 0x1d 0x1d 0x1d 0x1d 0x1d 0x02 0x0b 0x1d 0x1d 0x1d 0x1d 0x02 0x11 0x1d 0x1d 0x1d 0x1d 0x1d 0x02 0x17 0x1d 0x02 0x19 0x02 0x1a 0x02 0x1b 0x1d 0x1d 0x1d 0x1d 0x1d 0x1d 0x1d 0x1d 0x1d 0x1d 0x1d 0x1d 0x1d 0x1d 0x02 0x2a 0x02 0x2b 0x02 0x2c 0x02 0x2d 0x02 0x2e 0x1d 0x1d 0x02 0x31 0x02 0x32 0x02 0x33 0x02 0x34 0x02 0x35 0x02 0x36 0x02 0x37 0x1d 0x1d 0x1d 0x08 0x01 0x1d 0x08 0x05 0x08 0x06 0x08 0x07 0x08 0x04 0x08 0x09 0x08 0x0c 0x08 0x0f 0x08 0x10 0x08 0x12 0x08 0x14 0x08 0x15 0x08 0x16 0x08 0x17 0x08 0x19 0x08 0x1a 0x1d 0x08 0x1d 0x08 0x1e 0x08 0x21 0x1d 0x08 0x24 0x08 0x25 0x1d 0x08 0x29 0x08 0x26 0x08 0x2b 0x08 0x2a 0x1d 0x08 0x31 0x1d 0x1d 0x1d 0x08 0x56 0x08 0x37 0x08 0x3d 0x08 0x3e 0x08 0x3f 0x08 0x45 0x08 0x41 0x08 0x46 0x08 0x47 0x08 0x48 0x08 0x49 0x08 0x4a 0x08 0x3a 0x1d 0x1d 0x1d 0x1d 0x08 0x52 0x1d 0x1d 0x1d 0x08 0x56 0x08 0x57 0x08 0x58 0x08 0x59 0x08 0x5a 0x08 0x5b 0x08 0x5c 0x08 0x5d 0x08 0x5e 0x08 0x5f 0x1d 0x1d 0x08 0x62 0x08 0x5e 0x1d 0x08 0x64 0x08 0x56 0x08 0x69 0x08 0x6a 0x08 0x6b 0x08 0x6c>;

clock-names = "0\01\02\03\04\05\06\07\08\09\010\011\012\013\014\015\016\017\018\019\020\021\022\023\024\025\026\027\028\029\030\031\032\033\034\035\036\037\038\039\040\041\042\043\044\045\046\047\048\049\050\051\052\053\054\055\056\057\058\059\060\061\062\063\064\065\066\067\068\069\070\071\072\073\074\075\076\077\078\079\080\081\082\083\084\085\086\087\088\089\090\091\092\093\094\095\096\097\098\099\0100\0101\0102\0103\0104\0105\0106\0107\0108\0109\0110\0111\0112\0113\0114\0115\0116\0117\0118\0119\0120\0121\0122\0123\0124\0125\0126\0127\0128\0129\0130\0131\0132\0133\0134\0135\0136\0137\0138\0139\0140\0141\0142\0143\0144\0145\0146\0147\0148\0149\0150\0151\0152\0153\0154\0155\0156\0157\0158\0159\0160\0161\0162\0163\0164\0165\0166\0167\0168\0169\0170\0171\0172\0173\0174\0175\0176\0177\0178\0179\0180\0181\0182\0183";

};

};

efuse@11f20000 {

compatible = "mediatek,efuse";

reg = <0x00 0x11f20000 0x00 0x1000>;

#address-cells = <0x01>;

#size-cells = <0x01>;

calib@274 {

reg = <0x274 0x0c>;

phandle = <0x06>;

};

calib@8dc {

reg = <0x8dc 0x10>;

phandle = <0x13>;

};

usb3-rx-imp@8c8 {

reg = <0x8c8 0x01>;

bits = <0x00 0x05>;

phandle = <0x1b>;

};

usb3-tx-imp@8c8 {

reg = <0x8c8 0x02>;

bits = <0x05 0x05>;

phandle = <0x1c>;

};

usb3-intr@8c9 {

reg = <0x8c9 0x01>;

bits = <0x02 0x06>;

phandle = <0x1a>;

};

};

audio-controller@11210000 {

compatible = "mediatek,mt79xx-audio";

reg = <0x00 0x11210000 0x00 0x9000>;

interrupts = <0x00 0x6a 0x04>;

clocks = <0x02 0x12 0x02 0x13 0x02 0x14 0x02 0x15 0x02 0x16 0x08 0x65>;

clock-names = "aud_bus_ck\0aud_26m_ck\0aud_l_ck\0aud_aud_ck\0aud_eg2_ck\0aud_sel";

assigned-clocks = <0x08 0x65 0x08 0x66 0x08 0x67 0x08 0x68>;

assigned-clock-parents = <0x08 0x10 0x08 0x12 0x08 0x10 0x08 0x12>;

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <0x1e>;

phandle = <0x20>;

};

ice_debug {

compatible = "mediatek,mt7981-ice_debug\0mediatek,mt2701-ice_debug";

clocks = <0x02 0x18>;

clock-names = "ice_dbg";

};

chosen {

bootargs = "console=ttyS0,115200n1 loglevel=8 \t\t\t\tearlycon=uart8250,mmio32,0x11002000";

};

memory {

reg = <0x00 0x40000000 0x00 0x10000000>;

};

gpio-keys {

compatible = "gpio-keys";

reset {

label = "reset";

linux,code = <0x198>;

gpios = <0x0d 0x01 0x01>;

};

mesh {

label = "mesh";

linux,code = <0x100>;

gpios = <0x0d 0x00 0x00>;

};

hub {

label = "hub";

linux,code = <0x101>;

gpios = <0x0d 0x0c 0x00>;

};

};

gpio-leds {

compatible = "gpio-leds";

red {

label = "red";

gpios = <0x0d 0x09 0x00>;

};

green {

label = "green";

gpios = <0x0d 0x0a 0x01>;

};

blue {

label = "blue";

gpios = <0x0d 0x0b 0x01>;

};

4g {

label = "4g";

gpios = <0x0d 0x08 0x01>;

};

4g2 {

label = "4g2";

gpios = <0x0d 0x0d 0x01>;

};

};

gpio-export {

compatible = "gpio-export";

#size-cells = <0x00>;

wdg {

gpio-export,name = "wdg";

gpio-export,output = <0x01>;

gpios = <0x0d 0x02 0x00>;

};

pcie {

gpio-export,name = "pcie";

gpio-export,output = <0x01>;

gpios = <0x0d 0x03 0x00>;

};

4g1 {

gpio-export,name = "4g";

gpio-export,output = <0x01>;

gpios = <0x0d 0x04 0x00>;

};

4g2 {

gpio-export,name = "4g2";

gpio-export,output = <0x01>;

gpios = <0x0d 0x05 0x00>;

};

sim1 {

gpio-export,name = "sim1";

gpio-export,output = <0x01>;

gpios = <0x0d 0x06 0x00>;

};

sim2 {

gpio-export,name = "sim2";

gpio-export,output = <0x01>;

gpios = <0x0d 0x07 0x00>;

};

};

nmbm_spim_nand {

compatible = "generic,nmbm";

#address-cells = <0x01>;

#size-cells = <0x01>;

lower-mtd-device = <0x1f>;

forced-create;

partitions {

compatible = "fixed-partitions";

#address-cells = <0x01>;

#size-cells = <0x01>;

partition@0 {

label = "BL2";

reg = <0x00 0x100000>;

read-only;

};

partition@100000 {

label = "u-boot-env";

reg = <0x100000 0x80000>;

};

partition@180000 {

label = "Factory";

reg = <0x180000 0x200000>;

};

partition@380000 {

label = "FIP";

reg = <0x380000 0x200000>;

};

partition@580000 {

label = "ubi";

reg = <0x580000 0x4000000>;

};

};

};

sound_wm8960 {

compatible = "mediatek,mt79xx-wm8960-machine";

mediatek,platform = <0x20>;

audio-routing = "Headphone\0HP_L\0Headphone\0HP_R\0LINPUT1\0AMIC\0RINPUT1\0AMIC";

mediatek,audio-codec = <0x21>;

status = "disabled";

};

sound_si3218x {

compatible = "mediatek,mt79xx-si3218x-machine";

mediatek,platform = <0x20>;

mediatek,ext-codec = <0x22>;

status = "disabled";

};

};