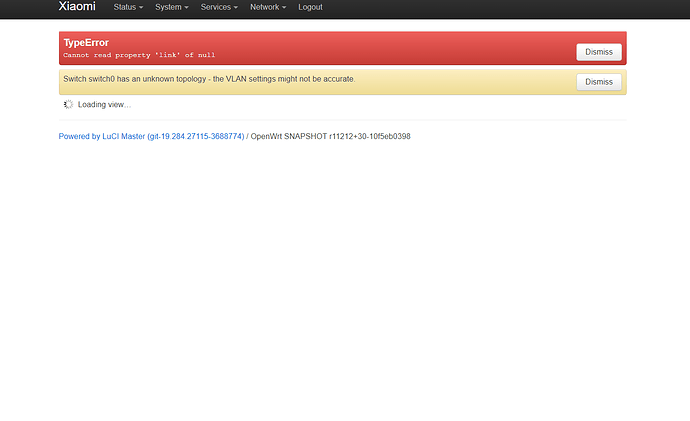

Anyone have a clue why I get this?

I meant that both of my routers have the same Mac addresses in wifi0, wifi1 and erh0.

Two routers - same Mac. This will break any network.

Are you experience the same problem?

I only have one so I don't get this problem.

The MAC address is extacted from the flash then one bit is changed for each interface so they shouldn't be the same on two different devices.

Mine are:

radio0: EC:41:18:C4:79:0E

radio1: EC:41:18:C4:79:0F

Following this thread it seems that the MAC address is stored in the u-boot environment. If you written the same image to both routers with your flash programmer, they will get the same MAC address. You are supposed to extract-modify-write the image from each router to retain the MAC address setting. Could this be the cause?

There is also a normal_firmware_md5= and a SN= setting.

could anyone dump the content of th flash-chip and upload the file here, please?

I need it is a master to modify the mac adresses AND the model.

In my dumb I can get the mac fixed, but the model is set to r3gv2 and I cannot set it to r4a, which is shorter (don't know how to use a hex editor properly).

@rogerpueyo: can I get your dump, please?

I noticed that the switch is missing from the menu "Network" in OpenWrt.

On the mi router 3g (v1) the switch can be seen.

On the cli I can see that the switch is properly being detected:

root@XiaomiWifiR4A:/# ls -l /sys/class/net

lrwxrwxrwx 1 root root 0 Oct 13 19:26 br-lan -> ../../devices/virtual/net/br-lan

lrwxrwxrwx 1 root root 0 Jan 1 1970 eth0 -> ../../devices/platform/1e100000.ethernet/net/eth0

lrwxrwxrwx 1 root root 0 Oct 13 19:26 ifb0 -> ../../devices/virtual/net/ifb0

lrwxrwxrwx 1 root root 0 Oct 13 19:26 ifb1 -> ../../devices/virtual/net/ifb1

lrwxrwxrwx 1 root root 0 Jan 1 1970 lo -> ../../devices/virtual/net/lo

lrwxrwxrwx 1 root root 0 Oct 13 19:26 wlan0 -> ../../devices/pci0000:00/0000:00:01.0/0000:02:00.0/net/wlan0

lrwxrwxrwx 1 root root 0 Oct 13 19:26 wlan1 -> ../../devices/pci0000:00/0000:00:00.0/0000:01:00.0/net/wlan1

The switch is a mt7530:

root@XiaomiWifiR4A:/# swconfig list

Found: switch0 - mt7530

More details:

root@XiaomiWifiR4A:/# swconfig dev switch0 show

Global attributes:

enable_vlan: 0

mib: Switch MIB counters

PPE_AC_BCNT0: 0

PPE_AC_PCNT0: 0

PPE_AC_BCNT63: 0

PPE_AC_PCNT63: 0

PPE_MTR_CNT0: 0

PPE_MTR_CNT63: 0

GDM1_TX_GBCNT: 0

GDM1_TX_GPCNT: 0

GDM1_TX_SKIPCNT: 0

GDM1_TX_COLCNT: 0

GDM1_RX_GBCNT1: 0

GDM1_RX_GPCNT1: 0

GDM1_RX_OERCNT: 0

GDM1_RX_FERCNT: 0

GDM1_RX_SERCNT: 0

GDM1_RX_LERCNT: 0

GDM1_RX_CERCNT: 0

GDM1_RX_FCCNT: 0

GDM2_TX_GBCNT: 0

GDM2_TX_GPCNT: 0

GDM2_TX_SKIPCNT: 0

GDM2_TX_COLCNT: 0

GDM2_RX_GBCNT: 0

GDM2_RX_GPCNT: 0

GDM2_RX_OERCNT: 0

GDM2_RX_FERCNT: 0

GDM2_RX_SERCNT: 0

GDM2_RX_LERCNT: 0

GDM2_RX_CERCNT: 0

GDM2_RX_FCCNT: 0

enable_mirror_rx: 0

enable_mirror_tx: 0

mirror_monitor_port: 0

mirror_source_port: 0

Port 0:

mib: Port 0 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 0

TxMulti : 0

TxBroad : 0

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 0

Tx65Byte : 0

Tx128Byte : 0

Tx256Byte : 0

Tx512Byte : 0

Tx1024Byte : 0

TxByte : 0

RxDrop : 0

RxFiltered : 0

RxUni : 0

RxMulti : 0

RxBroad : 0

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 0

Rx65Byte : 0

Rx128Byte : 0

Rx256Byte : 0

Rx512Byte : 0

Rx1024Byte : 0

RxByte : 0

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 1

link: port:0 link:down

Port 1:

mib: Port 1 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 0

TxMulti : 0

TxBroad : 0

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 0

Tx65Byte : 0

Tx128Byte : 0

Tx256Byte : 0

Tx512Byte : 0

Tx1024Byte : 0

TxByte : 0

RxDrop : 0

RxFiltered : 0

RxUni : 0

RxMulti : 0

RxBroad : 0

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 0

Rx65Byte : 0

Rx128Byte : 0

Rx256Byte : 0

Rx512Byte : 0

Rx1024Byte : 0

RxByte : 0

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 1

link: port:1 link:down

Port 2:

mib: Port 2 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 1999

TxMulti : 48

TxBroad : 7

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 789

Tx65Byte : 650

Tx128Byte : 258

Tx256Byte : 67

Tx512Byte : 97

Tx1024Byte : 193

TxByte : 510695

RxDrop : 0

RxFiltered : 0

RxUni : 1990

RxMulti : 593

RxBroad : 610

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 986

Rx65Byte : 1144

Rx128Byte : 378

Rx256Byte : 186

Rx512Byte : 135

Rx1024Byte : 364

RxByte : 890268

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 1

link: port:2 link:up speed:1000baseT full-duplex

Port 3:

mib: Port 3 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 0

TxMulti : 0

TxBroad : 0

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 0

Tx65Byte : 0

Tx128Byte : 0

Tx256Byte : 0

Tx512Byte : 0

Tx1024Byte : 0

TxByte : 0

RxDrop : 0

RxFiltered : 0

RxUni : 0

RxMulti : 0

RxBroad : 0

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 0

Rx65Byte : 0

Rx128Byte : 0

Rx256Byte : 0

Rx512Byte : 0

Rx1024Byte : 0

RxByte : 0

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 1

link: port:3 link:down

Port 4:

mib: Port 4 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 0

TxMulti : 0

TxBroad : 0

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 0

Tx65Byte : 0

Tx128Byte : 0

Tx256Byte : 0

Tx512Byte : 0

Tx1024Byte : 0

TxByte : 0

RxDrop : 0

RxFiltered : 0

RxUni : 0

RxMulti : 0

RxBroad : 0

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 0

Rx65Byte : 0

Rx128Byte : 0

Rx256Byte : 0

Rx512Byte : 0

Rx1024Byte : 0

RxByte : 0

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 2

link: port:4 link:down

Port 5:

mib: Port 5 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 0

TxMulti : 0

TxBroad : 0

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 0

Tx65Byte : 0

Tx128Byte : 0

Tx256Byte : 0

Tx512Byte : 0

Tx1024Byte : 0

TxByte : 0

RxDrop : 0

RxFiltered : 0

RxUni : 0

RxMulti : 0

RxBroad : 0

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 0

Rx65Byte : 0

Rx128Byte : 0

Rx256Byte : 0

Rx512Byte : 0

Rx1024Byte : 0

RxByte : 0

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 1

link: port:5 link:down

Port 6:

mib: Port 6 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 1996

TxMulti : 594

TxBroad : 612

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 990

Tx65Byte : 1147

Tx128Byte : 378

Tx256Byte : 186

Tx512Byte : 137

Tx1024Byte : 364

TxByte : 892027

RxDrop : 0

RxFiltered : 50

RxUni : 2007

RxMulti : 77

RxBroad : 25

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 795

Rx65Byte : 672

Rx128Byte : 268

Rx256Byte : 83

Rx512Byte : 97

Rx1024Byte : 194

RxByte : 521195

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 1

link: port:6 link:up speed:1000baseT full-duplex

Port 7:

mib: Port 7 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 0

TxMulti : 0

TxBroad : 0

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 0

Tx65Byte : 0

Tx128Byte : 0

Tx256Byte : 0

Tx512Byte : 0

Tx1024Byte : 0

TxByte : 0

RxDrop : 0

RxFiltered : 0

RxUni : 0

RxMulti : 0

RxBroad : 0

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 0

Rx65Byte : 0

Rx128Byte : 0

Rx256Byte : 0

Rx512Byte : 0

Rx1024Byte : 0

RxByte : 0

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:7 link:down

VLAN 1:

vid: 1

ports: 0 1 2 3 5 6t

VLAN 2:

vid: 2

ports: 4 6t

root@XiaomiWifiR4A:/# swconfig dev switch0 show

Global attributes:

enable_vlan: 0

mib: Switch MIB counters

PPE_AC_BCNT0: 0

PPE_AC_PCNT0: 0

PPE_AC_BCNT63: 0

PPE_AC_PCNT63: 0

PPE_MTR_CNT0: 0

PPE_MTR_CNT63: 0

GDM1_TX_GBCNT: 0

GDM1_TX_GPCNT: 0

GDM1_TX_SKIPCNT: 0

GDM1_TX_COLCNT: 0

GDM1_RX_GBCNT1: 0

GDM1_RX_GPCNT1: 0

GDM1_RX_OERCNT: 0

GDM1_RX_FERCNT: 0

GDM1_RX_SERCNT: 0

GDM1_RX_LERCNT: 0

GDM1_RX_CERCNT: 0

GDM1_RX_FCCNT: 0

GDM2_TX_GBCNT: 0

GDM2_TX_GPCNT: 0

GDM2_TX_SKIPCNT: 0

GDM2_TX_COLCNT: 0

GDM2_RX_GBCNT: 0

GDM2_RX_GPCNT: 0

GDM2_RX_OERCNT: 0

GDM2_RX_FERCNT: 0

GDM2_RX_SERCNT: 0

GDM2_RX_LERCNT: 0

GDM2_RX_CERCNT: 0

GDM2_RX_FCCNT: 0

enable_mirror_rx: 0

enable_mirror_tx: 0

mirror_monitor_port: 0

mirror_source_port: 0

Port 0:

mib: Port 0 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 0

TxMulti : 0

TxBroad : 0

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 0

Tx65Byte : 0

Tx128Byte : 0

Tx256Byte : 0

Tx512Byte : 0

Tx1024Byte : 0

TxByte : 0

RxDrop : 0

RxFiltered : 0

RxUni : 0

RxMulti : 0

RxBroad : 0

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 0

Rx65Byte : 0

Rx128Byte : 0

Rx256Byte : 0

Rx512Byte : 0

Rx1024Byte : 0

RxByte : 0

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 1

link: port:0 link:down

Port 1:

mib: Port 1 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 0

TxMulti : 0

TxBroad : 0

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 0

Tx65Byte : 0

Tx128Byte : 0

Tx256Byte : 0

Tx512Byte : 0

Tx1024Byte : 0

TxByte : 0

RxDrop : 0

RxFiltered : 0

RxUni : 0

RxMulti : 0

RxBroad : 0

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 0

Rx65Byte : 0

Rx128Byte : 0

Rx256Byte : 0

Rx512Byte : 0

Rx1024Byte : 0

RxByte : 0

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 1

link: port:1 link:down

Port 2:

mib: Port 2 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 2708

TxMulti : 72

TxBroad : 7

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 1235

Tx65Byte : 815

Tx128Byte : 367

Tx256Byte : 76

Tx512Byte : 101

Tx1024Byte : 193

TxByte : 577102

RxDrop : 0

RxFiltered : 0

RxUni : 2990

RxMulti : 922

RxBroad : 956

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 1393

Rx65Byte : 1610

Rx128Byte : 598

Rx256Byte : 381

Rx512Byte : 150

Rx1024Byte : 736

RxByte : 1592118

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 1

link: port:2 link:up speed:1000baseT full-duplex

Port 3:

mib: Port 3 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 0

TxMulti : 0

TxBroad : 0

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 0

Tx65Byte : 0

Tx128Byte : 0

Tx256Byte : 0

Tx512Byte : 0

Tx1024Byte : 0

TxByte : 0

RxDrop : 0

RxFiltered : 0

RxUni : 0

RxMulti : 0

RxBroad : 0

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 0

Rx65Byte : 0

Rx128Byte : 0

Rx256Byte : 0

Rx512Byte : 0

Rx1024Byte : 0

RxByte : 0

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 1

link: port:3 link:down

Port 4:

mib: Port 4 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 0

TxMulti : 0

TxBroad : 0

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 0

Tx65Byte : 0

Tx128Byte : 0

Tx256Byte : 0

Tx512Byte : 0

Tx1024Byte : 0

TxByte : 0

RxDrop : 0

RxFiltered : 0

RxUni : 0

RxMulti : 0

RxBroad : 0

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 0

Rx65Byte : 0

Rx128Byte : 0

Rx256Byte : 0

Rx512Byte : 0

Rx1024Byte : 0

RxByte : 0

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 2

link: port:4 link:down

Port 5:

mib: Port 5 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 0

TxMulti : 0

TxBroad : 0

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 0

Tx65Byte : 0

Tx128Byte : 0

Tx256Byte : 0

Tx512Byte : 0

Tx1024Byte : 0

TxByte : 0

RxDrop : 0

RxFiltered : 0

RxUni : 0

RxMulti : 0

RxBroad : 0

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 0

Rx65Byte : 0

Rx128Byte : 0

Rx256Byte : 0

Rx512Byte : 0

Rx1024Byte : 0

RxByte : 0

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 1

link: port:5 link:down

Port 6:

mib: Port 6 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 2990

TxMulti : 922

TxBroad : 956

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 1393

Tx65Byte : 1610

Tx128Byte : 598

Tx256Byte : 381

Tx512Byte : 150

Tx1024Byte : 736

TxByte : 1592118

RxDrop : 0

RxFiltered : 50

RxUni : 2711

RxMulti : 101

RxBroad : 25

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 1239

Rx65Byte : 835

Rx128Byte : 376

Rx256Byte : 92

Rx512Byte : 101

Rx1024Byte : 194

RxByte : 587149

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 1

link: port:6 link:up speed:1000baseT full-duplex

Port 7:

mib: Port 7 MIB counters

TxDrop : 0

TxCRC : 0

TxUni : 0

TxMulti : 0

TxBroad : 0

TxCollision: 0

TxSingleCol: 0

TxMultiCol : 0

TxDefer : 0

TxLateCol : 0

TxExcCol : 0

TxPause : 0

Tx64Byte : 0

Tx65Byte : 0

Tx128Byte : 0

Tx256Byte : 0

Tx512Byte : 0

Tx1024Byte : 0

TxByte : 0

RxDrop : 0

RxFiltered : 0

RxUni : 0

RxMulti : 0

RxBroad : 0

RxAlignErr : 0

RxCRC : 0

RxUnderSize: 0

RxFragment : 0

RxOverSize : 0

RxJabber : 0

RxPause : 0

Rx64Byte : 0

Rx65Byte : 0

Rx128Byte : 0

Rx256Byte : 0

Rx512Byte : 0

Rx1024Byte : 0

RxByte : 0

RxCtrlDrop : 0

RxIngDrop : 0

RxARLDrop : 0

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:7 link:down

VLAN 1:

vid: 1

ports: 0 1 2 3 5 6t

VLAN 2:

vid: 2

ports: 4 6t

As one can see there are vlans configured.

I don't know why the openwrt gui doesn't recognize the switch.

According to this thread, the file /etc/board.d/02_network must be adjusted so that it works with the R4A.

It's my fault sorry.

The latest build linked is causing this.

I've a new build that has this bug solved.

I'll upload it to my drive when I get a chance.

New build

The switch works with your new build from 15-10-19  Good job!

Good job!

The WAN-port had a different naming compared to the mi router 3g, so you cannot copy configs 1:1 without modifying them. I need to analyze this further.

I found a problem with ssh-logins: they are not possible with a public key, because the file /etc/dropbear/authorized_keys is writable by group and others, you must perform a "chmod g-w o-w" on it. It would be great to receive a fix for the next build.

Edited:

nvm i used the wrong socket for the SOIC8 clip. now im getting a "No EEPROM/flash device found" soo it seems that i really need to plug the CH341a 3.3.v to the Router. oh well going to order a dupont cable

It's because I pulled rogerpueyo's PR and the earlier builds were based on a different patch. The switch layout is slightly different.

I also fell for the 3.3 volts, but they're not necessary. If you get the no EEPROM-error, something is wrong with the connection. Try to reattache the clip.

When flashing, one can see erase-errors - their root cause also is a clip that's not properly attached.

ahhh i see, i'll try it again later

Ok i was able to flash the edited .bin file to my router via CH341a spi, softbricked my router while doing it as well LOL because the spi flasher keeps on disconnecting had to switch it to my other USB port and it worked.

It got bricked when the flasher was done erasing the chip and was about to write the edited bin then suddenly the USB disconnected.

Anyway i got it back up and working, only step left is the serial port. Can anyone show me a picture on how you guys connect the USB serial port to the router?? also i've read that the black Ch341a programmer has a UART mode can anyone shed some light on how to us it so i dont have to get a USB to serial port adapter LOL!

Thanks!

Usually there is a jumper connector on the flasher to switch between flasher mode and TTL UART adapter mode. If I'm not mistaken, in mine, short pins 1-2 for flasher mode and short pins 2-3 for TTL UART adapter mode. If in doubt, please post pictures of your flasher (from the top and from below).

And yes, the USB port you connect it may make a big difference (for example some may not have enough power for some reason but others do).

Heres my Ch341a mini programmer. By jumper connector you mean the yellow sleeve?

once i switch the jumper connector to pins 2-3 what should i do next to connect it to the router?

Thanks!

Looks like It's the same as mine (see the pictures I put earlier on the thread).

Yes, the yellow connector, to switch to TTL UART mode you need to switch it to jumpers 2-3. When you connect it back to the computer, on Linux you should see a new /dev/ttyUSB(something) device, on windows you should see a new COM port appear.

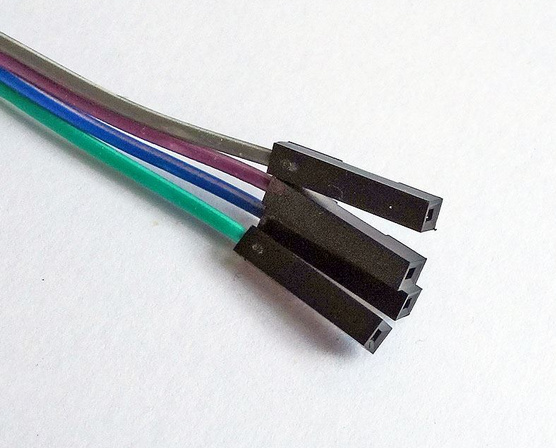

Then you'll need some cables with "dupont" connectors, like these:

Connect them to connect to the TXD, RXD and GND pins on that same row, to (respectively) the RXD, TXD and GND UART pins on the router's board. They are shown in the first posts, these are the ones:

https://forum.openwrt.org/uploads/default/original/2X/0/083791d2baf442f1fbc8ae18e5d99fa0b9cb0c66.jpeg

Unless you want to do some soldering, you'll probably need something like these pin headers (for me, they came with the flasher):

You shouldn't need to solder them, as usually just placing this piece with 4 pins on top of the router's UART port holes just fits and makes enough contact (it did for me). Then use dupont (female to female) cables to connect the flasher to these pin headers, and thus to the router's UART port. This is how I did it, but you should be able to get the general idea should you want to do some other way.

Important:

- do NOT connect the VCC pin, you only need to connect the other 3

- GND connects to GND on the other side

- TX from one side should connect to RX on the other side and vice versa

Finally use a terminal emulator (like putty on windows, or like minicom or screen on Linux, or equivalent on Mac) connected to the COM / ttyUSB port of the TTL adapter with baud rate 115200, and when you power on the router you should see its console and be able to interact with it like described in the first posts.

thanks! i'll purchase dupont connectors today.

@araujorm thanks for the help! was able to successfully flash the router to Openwrt! the 4 pin that came with my flasher didn't fit the holes for the TX and RT port had to grab the 4 pin that came with my faulty CH341a programmer.

There is a report at https://www.ise.io/whitepaper/sohopelessly-broken-2/ about how to get shell access on a Mi Router 3. Maybe something like that is present on 4A too? Or not, it was reported to Xiaomi late 2018 so it might be already fixed in the oldest available firmware.