From what I can tell, its on RGMII2, MDIO, PHY address 29 (https://github.com/Lochnair/kernel_e50/blob/v2.0.9/master/drivers/net/ethernet/realtek/rtl8367c/smi.c#L38). But, this is what others have related who looked at it, so take it as hearsay.

GMAC1 is status = "disabled" in the dtsi (either the ERx or the mt7621.dtsi, I don't remember offhand)

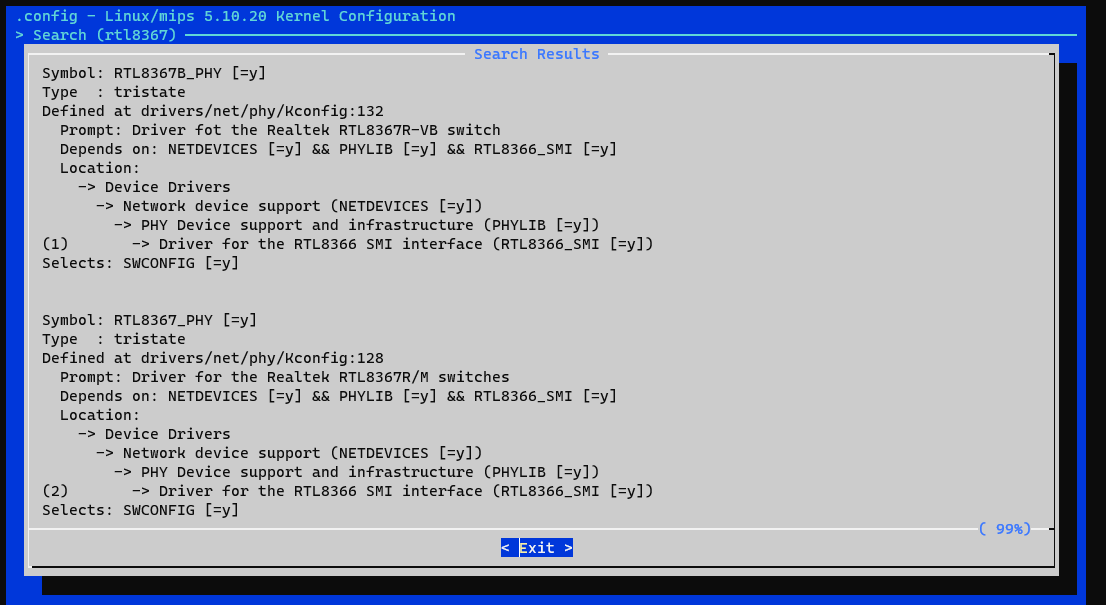

Is there an actual DSA driver available for the RTL8367RB? I don't mind trying to port it over if I had a place to start.

I'm willing to do whatever testing and grunt work. Building the image takes almost no time at all, and flashing to test is even faster (I've been just TFTP'ing to RAM to boot)

This is the EdgeOS v2 stock DTS on whatever kernel version it ships with

Warning (unit_address_vs_reg): Node /pcie@1e140000/pcie2 has a reg or ranges property, but no unit name

Warning (unit_address_vs_reg): Node /pcie@1e140000/pcie0 has a reg or ranges property, but no unit name

Warning (unit_address_vs_reg): Node /pcie@1e140000/pcie1 has a reg or ranges property, but no unit name

Warning (unit_address_vs_reg): Node /cpuintc@0 has a unit name, but no reg property

Warning (unit_address_vs_reg): Node /sysclock@0 has a unit name, but no reg property

Warning (unit_address_vs_reg): Node /cpuclock@0 has a unit name, but no reg property

Warning (unit_address_vs_reg): Node /cpus/cpu@1 has a unit name, but no reg property

Warning (unit_address_vs_reg): Node /cpus/cpu@0 has a unit name, but no reg property

/dts-v1/;

/ {

compatible = "ubiquiti,edgerouter";

model = "Ubiquiti EdgeRouter";

#address-cells = <0x1>;

#size-cells = <0x1>;

palmbus@1E000000 {

compatible = "palmbus";

ranges = <0x0 0x1e000000 0xfffff>;

#address-cells = <0x1>;

#size-cells = <0x1>;

phandle = <0x10>;

reg = <0x1e000000 0x100000>;

linux,phandle = <0x10>;

sysc@0 {

compatible = "mtk,mt7621-sysc";

phandle = <0x11>;

reg = <0x0 0x100>;

linux,phandle = <0x11>;

};

wdt@100 {

compatible = "mtk,mt7621-wdt";

phandle = <0x12>;

reg = <0x100 0x100>;

linux,phandle = <0x12>;

};

mc@1fbf8000 {

compatible = "mtk,mt7621-mc";

phandle = <0x19>;

reg = <0x1fbf8000 0x8000>;

linux,phandle = <0x19>;

};

i2c@900 {

compatible = "mediatek,mt7621-i2c";

clocks = <0x1>;

resets = <0x2 0x10>;

status = "okay";

#address-cells = <0x1>;

#size-cells = <0x0>;

phandle = <0x15>;

reg = <0x900 0x100>;

pinctrl-0 = <0x3>;

reset-names = "i2c";

linux,phandle = <0x15>;

pinctrl-names = "default";

pca9555@25 {

compatible = "nxp,pca9555";

status = "okay";

phandle = <0xe>;

reg = <0x25>;

#gpio-cells = <0x2>;

linux,phandle = <0xe>;

};

};

gpio@600 {

compatible = "mtk,mt7621-gpio";

#address-cells = <0x1>;

#size-cells = <0x0>;

reg = <0x600 0x100>;

bank@1 {

compatible = "mtk,mt7621-gpio-bank";

gpio-controller;

phandle = <0x13>;

reg = <0x1>;

#gpio-cells = <0x2>;

linux,phandle = <0x13>;

};

bank@2 {

compatible = "mtk,mt7621-gpio-bank";

gpio-controller;

phandle = <0x14>;

reg = <0x2>;

#gpio-cells = <0x2>;

linux,phandle = <0x14>;

};

bank@0 {

compatible = "mtk,mt7621-gpio-bank";

gpio-controller;

phandle = <0xd>;

reg = <0x0>;

#gpio-cells = <0x2>;

linux,phandle = <0xd>;

};

};

hsdma@7000 {

#dma-cells = <0x1>;

compatible = "mediatek,mt7621-hsdma";

resets = <0x2 0x5>;

#dma-requests = <0x1>;

status = "disabled";

interrupt-parent = <0x4>;

interrupts = <0x0 0xb 0x4>;

phandle = <0x1c>;

reg = <0x7000 0x1000>;

reset-names = "hsdma";

linux,phandle = <0x1c>;

#dma-channels = <0x1>;

};

memc@5000 {

compatible = "mtk,mt7621-memc";

phandle = <0x17>;

reg = <0x300 0x100>;

linux,phandle = <0x17>;

};

uartlite@c00 {

reg-io-width = <0x4>;

compatible = "ns16550a";

clocks = <0x1>;

interrupt-parent = <0x4>;

interrupts = <0x0 0x1a 0x4>;

phandle = <0x1a>;

reg = <0xc00 0x100>;

clock-frequency = <0x2faf080>;

reg-shift = <0x2>;

linux,phandle = <0x1a>;

no-loopback-test;

};

spi@b00 {

compatible = "ralink,mt7621-spi";

clocks = <0x1>;

resets = <0x2 0x12>;

status = "disabled";

#address-cells = <0x1>;

#size-cells = <0x0>;

phandle = <0x1b>;

reg = <0xb00 0x100>;

pinctrl-0 = <0x6>;

reset-names = "spi";

linux,phandle = <0x1b>;

pinctrl-names = "default";

};

i2s@a00 {

compatible = "mediatek,mt7621-i2s";

clocks = <0x1>;

resets = <0x2 0x11>;

txdma-req = <0x2>;

status = "disabled";

interrupt-parent = <0x4>;

interrupts = <0x0 0x10 0x4>;

dma-names = "tx", "rx";

phandle = <0x16>;

rxdma-req = <0x3>;

reg = <0xa00 0x100>;

dmas = <0x5 0x4 0x5 0x6>;

reset-names = "i2s";

linux,phandle = <0x16>;

};

gdma@2800 {

#dma-cells = <0x1>;

compatible = "ralink,rt3883-gdma";

resets = <0x2 0xe>;

#dma-requests = <0x10>;

status = "disabled";

interrupt-parent = <0x4>;

interrupts = <0x0 0xd 0x4>;

phandle = <0x5>;

reg = <0x2800 0x800>;

reset-names = "dma";

linux,phandle = <0x5>;

#dma-channels = <0x10>;

};

cpc@1fbf0000 {

compatible = "mtk,mt7621-cpc";

phandle = <0x18>;

reg = <0x1fbf0000 0x8000>;

linux,phandle = <0x18>;

};

};

nand@1e003000 {

compatible = "mtk,mt7621-nand";

status = "okay";

#address-cells = <0x1>;

bank-width = <0x2>;

#size-cells = <0x1>;

phandle = <0x28>;

reg = <0x1e003000 0x800 0x1e003800 0x800>;

linux,phandle = <0x28>;

partition@0 {

read-only;

label = "ALL";

reg = <0x0 0x0>;

};

partition@e0000 {

label = "eeprom";

phandle = <0xa>;

reg = <0xe0000 0x60000>;

linux,phandle = <0xa>;

};

partition@440000 {

label = "Kernel2";

reg = <0x440000 0x300000>;

};

partition@80000 {

read-only;

label = "Config";

reg = <0x80000 0x60000>;

};

partition@1 {

read-only;

label = "ALL";

reg = <0x0 0x0>;

};

partition@140000 {

label = "Kernel1";

reg = <0x140000 0x300000>;

};

partition@740000 {

label = "RootFS";

reg = <0x740000 0x1f4c0000>;

};

partition@2 {

label = "Bootloader";

reg = <0x0 0x80000>;

};

};

sdhci@1E130000 {

compatible = "ralink,mt7620-sdhci";

status = "okay";

interrupt-parent = <0x4>;

interrupts = <0x0 0x14 0x4>;

phandle = <0x26>;

reg = <0x1e130000 0x4000>;

linux,phandle = <0x26>;

};

ethernet@1e100000 {

compatible = "mediatek,mt7621-eth";

mac-address = [74 ac b9 eb 43 75];

resets = <0x2 0x6 0x2 0x17>;

mediatek,ethsys = <0x2b>;

mediatek,switch = <0x9>;

interrupt-parent = <0x4>;

#address-cells = <0x1>;

interrupts = <0x0 0x3 0x4>;

#size-cells = <0x0>;

phandle = <0x29>;

reg = <0x1e100000 0x10000>;

mtd-mac-address = <0xa 0x22>;

reset-names = "fe", "eth";

linux,phandle = <0x29>;

mdio-bus {

#address-cells = <0x1>;

#size-cells = <0x0>;

ethernet-phy@1f {

phandle = <0x2a>;

reg = <0x1f>;

phy-mode = "rgmii";

linux,phandle = <0x2a>;

};

};

};

clkctrl {

compatible = "ralink,rt2880-clock";

#clock-cells = <0x1>;

phandle = <0xc>;

linux,phandle = <0xc>;

};

__symbols__ {

gpio2 = "/palmbus@1E000000/gpio@600/bank@2";

sdhci_pins = "/pinctrl/sdhci";

gpio0 = "/palmbus@1E000000/gpio@600/bank@0";

nand_pins = "/pinctrl/nand";

spi0 = "/palmbus@1E000000/spi@b00";

memc = "/palmbus@1E000000/memc@5000";

uartlite = "/palmbus@1E000000/uartlite@c00";

sdhci = "/sdhci@1E130000";

sysclock = "/sysclock@0";

clkctrl = "/clkctrl";

rgmii2_pins = "/pinctrl/rgmii2";

xhci = "/xhci@1E1C0000";

ethsys = "/syscon@1e000000";

spi_pins = "/pinctrl/spi";

uart3_pins = "/pinctrl/uart3";

cpuintc = "/cpuintc@0";

hsdma = "/palmbus@1E000000/hsdma@7000";

gic = "/interrupt-controller@1fbc0000";

rgmii1_pins = "/pinctrl/rgmii1";

leds = "/leds";

palmbus = "/palmbus@1E000000";

uart2_pins = "/pinctrl/uart2";

state_default = "/pinctrl/pinctrl0";

phy1f = "/ethernet@1e100000/mdio-bus/ethernet-phy@1f";

nand = "/nand@1e003000";

ethernet = "/ethernet@1e100000";

pcie = "/pcie@1e140000";

gpio_i2c_25 = "/palmbus@1E000000/i2c@900/pca9555@25";

wdt = "/palmbus@1E000000/wdt@100";

uart1_pins = "/pinctrl/uart1";

gpio1 = "/palmbus@1E000000/gpio@600/bank@1";

i2s = "/palmbus@1E000000/i2s@a00";

gdma = "/palmbus@1E000000/gdma@2800";

pcie_pins = "/pinctrl/pcie";

i2c_pins = "/pinctrl/i2c";

cpuclock = "/cpuclock@0";

mc = "/palmbus@1E000000/mc@1fbf8000";

factory = "/nand@1e003000/partition@e0000";

cpc = "/palmbus@1E000000/cpc@1fbf0000";

sysc = "/palmbus@1E000000/sysc@0";

rstctrl = "/rstctrl";

pinctrl = "/pinctrl";

i2c = "/palmbus@1E000000/i2c@900";

gsw = "/gsw@1e110000";

mdio_pins = "/pinctrl/mdio";

};

pcie@1e140000 {

compatible = "mediatek,mt7621-pci";

clocks = <0xc 0x18 0xc 0x19 0xc 0x1a>;

resets = <0x2 0x18 0x2 0x19 0x2 0x1a>;

device_type = "pci";

clock-names = "pcie0", "pcie1", "pcie2";

ranges = <0x2000000 0x0 0x0 0x60000000 0x0 0x10000000 0x1000000 0x0 0x0 0x1e160000 0x0 0x10000>;

status = "okay";

bus-range = <0x0 0xff>;

interrupt-parent = <0x4>;

#address-cells = <0x3>;

interrupts = <0x0 0x4 0x4 0x0 0x18 0x4 0x0 0x19 0x4>;

#size-cells = <0x2>;

phandle = <0x2c>;

reg = <0x1e140000 0x100 0x1e142000 0x100>;

pinctrl-0 = <0xb>;

reset-names = "pcie0", "pcie1", "pcie2";

linux,phandle = <0x2c>;

pinctrl-names = "default";

pcie2 {

device_type = "pci";

#address-cells = <0x3>;

#size-cells = <0x2>;

reg = <0x1000 0x0 0x0 0x0 0x0>;

};

pcie0 {

device_type = "pci";

#address-cells = <0x3>;

#size-cells = <0x2>;

reg = <0x0 0x0 0x0 0x0 0x0>;

};

pcie1 {

device_type = "pci";

#address-cells = <0x3>;

#size-cells = <0x2>;

reg = <0x800 0x0 0x0 0x0 0x0>;

};

};

leds {

compatible = "gpio-leds";

phandle = <0x2d>;

linux,phandle = <0x2d>;

pwr_blue {

gpios = <0xe 0x10 0x0>;

default-state = "on";

};

pwr_white {

gpios = <0xe 0xd 0x0>;

default-state = "off";

};

};

aliases {

serial1 = "/palmbus@1E000000/uartlite@c00";

};

cpuintc@0 {

compatible = "mti,cpu-interrupt-controller";

#interrupt-cells = <0x1>;

#address-cells = <0x0>;

phandle = <0xf>;

linux,phandle = <0xf>;

interrupt-controller;

};

sysclock@0 {

compatible = "fixed-clock";

#clock-cells = <0x0>;

phandle = <0x1>;

clock-frequency = <0x2faf080>;

linux,phandle = <0x1>;

};

gsw@1e110000 {

compatible = "mediatek,mt7621-gsw";

interrupt-parent = <0x4>;

interrupts = <0x0 0x17 0x4 0x0 0xc 0x4>;

phandle = <0x9>;

reg = <0x1e110000 0x8000>;

linux,phandle = <0x9>;

interrupt-names = "gsw", "rtl8367_int";

};

xhci@1E1C0000 {

compatible = "mediatek,mt8173-xhci";

clocks = <0x1>;

clock-names = "sys_ck";

status = "okay";

interrupt-parent = <0x4>;

interrupts = <0x0 0x16 0x4>;

phandle = <0x27>;

reg = <0x1e1c0000 0x1000 0x1e1d0700 0x100>;

linux,phandle = <0x27>;

};

interrupt-controller@1fbc0000 {

compatible = "mti,gic";

#interrupt-cells = <0x3>;

mti,reserved-cpu-vectors = <0x7>;

phandle = <0x4>;

reg = <0x1fbc0000 0x2000>;

linux,phandle = <0x4>;

interrupt-controller;

timer {

compatible = "mti,gic-timer";

clocks = <0x8>;

interrupts = <0x1 0x1 0x0>;

};

};

gpio-keys-polled {

compatible = "gpio-keys-polled";

poll-interval = <0x14>;

#address-cells = <0x1>;

#size-cells = <0x0>;

reset {

gpios = <0xd 0xc 0x1>;

label = "reset";

linux,code = <0x198>;

};

};

cpuclock@0 {

compatible = "fixed-clock";

#clock-cells = <0x0>;

phandle = <0x8>;

clock-frequency = <0x3473bc00>;

linux,phandle = <0x8>;

};

syscon@1e000000 {

compatible = "mediatek,mt7621-ethsys", "syscon";

#clock-cells = <0x1>;

phandle = <0x2b>;

reg = <0x1e000000 0x1000>;

linux,phandle = <0x2b>;

};

cpus {

cpu@1 {

compatible = "mips,mips1004Kc";

};

cpu@0 {

compatible = "mips,mips1004Kc";

};

};

rstctrl {

compatible = "ralink,rt2880-reset";

#reset-cells = <0x1>;

phandle = <0x2>;

linux,phandle = <0x2>;

};

pinctrl {

compatible = "ralink,rt2880-pinmux";

phandle = <0x1d>;

pinctrl-0 = <0x7>;

linux,phandle = <0x1d>;

pinctrl-names = "default";

mdio {

phandle = <0x23>;

linux,phandle = <0x23>;

mdio {

ralink,group = "mdio";

ralink,function = "mdio";

};

};

rgmii1 {

phandle = <0x21>;

linux,phandle = <0x21>;

rgmii1 {

ralink,group = "rgmii1";

ralink,function = "rgmii1";

};

};

sdhci {

phandle = <0x25>;

linux,phandle = <0x25>;

sdhci {

ralink,group = "sdhci";

ralink,function = "sdhci";

};

};

uart2 {

phandle = <0x1f>;

linux,phandle = <0x1f>;

uart2 {

ralink,group = "uart2";

ralink,function = "uart2";

};

};

nand {

phandle = <0x24>;

linux,phandle = <0x24>;

sdhci-nand {

ralink,group = "sdhci";

ralink,function = "nand2";

};

spi-nand {

ralink,group = "spi";

ralink,function = "nand1";

};

};

pinctrl0 {

phandle = <0x7>;

linux,phandle = <0x7>;

gpio {

ralink,group = "uart2", "uart3", "rgmii2", "sdhci";

ralink,function = "gpio";

};

};

spi {

phandle = <0x6>;

linux,phandle = <0x6>;

spi {

ralink,group = "spi";

ralink,function = "spi";

};

};

pcie {

phandle = <0xb>;

linux,phandle = <0xb>;

pcie {

ralink,group = "pcie";

ralink,function = "pcie rst";

};

};

rgmii2 {

phandle = <0x22>;

linux,phandle = <0x22>;

rgmii2 {

ralink,group = "rgmii2";

ralink,function = "rgmii2";

};

};

uart3 {

phandle = <0x20>;

linux,phandle = <0x20>;

uart3 {

ralink,group = "uart3";

ralink,function = "uart3";

};

};

uart1 {

phandle = <0x1e>;

linux,phandle = <0x1e>;

uart1 {

ralink,group = "uart1";

ralink,function = "uart1";

};

};

i2c {

phandle = <0x3>;

linux,phandle = <0x3>;

i2c {

ralink,group = "i2c";

ralink,function = "i2c";

};

};

};

};