(Moved to For Developers section.)

Hi I'll try with different wording found on 8devices Carambola2 forum,

think its the most proper wording to rephase my concept (I told You I am a real noob):"

Run eth0 and eth1 as part of AR9331 hardware switch

As far as I understand, the AR9331 has a 5-port internal hardware switch.

I would like to run the two physical ethernet ports which are rounted out of the Carambola2 to be handled both by the internal ethernet switch, having only one MAC port of the AR9331 talking to that switch. Does anyone know how to do this?

Why not just configure a software bridge using brctl on Linux? Well, software switching has higher latency and adds software load without any need.

Thanks in advance!"

Thanks

P.

Hi Psyborg,

while browsing the openwrt git looking for ar9331 based devices with more than two ethernet plug

I found the TP-LINK TL-WR940N v4 router

I found the switch paraghraph I found:

static void __init tl_wr940n_setup(void)

{

u8 *mac = (u8 *) KSEG1ADDR(0x1f01fc00);

u8 *ee = (u8 *) KSEG1ADDR(0x1fff1000);

ath79_register_m25p80(&tl_wr940n_flash_data);

ath79_register_mdio(0, 0x0);

ath79_init_mac(ath79_eth0_data.mac_addr, mac, 1);

ath79_init_mac(ath79_eth1_data.mac_addr, mac, -1);

ath79_switch_data.phy4_mii_en = 1;

ath79_register_eth(0);

ath79_register_eth(1);

ath79_register_wmac(ee, mac);

are these the registry key you were talking about ? I don't know where to find them and of course

how to set them for the ge0/mac0 reset the datasheet was talking about.

Cheers

P.

your device seem to be missing profile in target/linux/ar71xx/base-files/etc/board.d/02_network

adding something like this should work.

ucidef_set_interface_lan "eth1" "eth0"

ucidef_add_switch "switch0" \

"0@eth1" "1:lan:4" "2:lan:3" "3:lan:2" "4:lan:1"Hi Psyborg, sorry but I am not following please correct me if aI am wrong:

"UCI creates an abstraction layer for configuring network interfaces:

In /etc/config/network you allocate a name like lan or internet_wire or whatever to each ifname-variable for every device and then this name is consistently used through the entire UCI configuration. But this can only be used in conjunction with UCI!"

but I thought we were talking about devices (physical nic interfaces)

what I was thinking it was like booting up the routher with the 2 available physical ports of the switch

as two devices belonging to the switch as this makes sense according to the data sheet !

Unless the two interfaces are already connected by the switch and the datashhet is misleading.

Otherwise I am still in deep troubles trying to visualize the physical layout of the ar150 router.

Remember that all of this was to be able to mirror the data going thruough one port, to the second port

and use a PC connected to the 2nd port to analyze the traffic, and as far as I understood I can mirror traffic from one port to the other on a switch but not between unrelated unrelated ones.

Thanks

Best

P.

sorry but in one post you have ar150 in other some tplink and then carambola.. which device really are you trying to configure?

single port qca9531 - i was able to connect via (default) gmac0 and via switch on gmac1 by modifying 02_network and rebuilding

Hi Psyborg,

thank you for Your patience. I am very new to linux.. imagine about embedded ones.

ar150 uses 9330(or 9331)soc carambola2 uses the same chipset, TP-LINK TL-WR940N v4 too.

So my idea was to figure out the difference between the 3 machines surfing the openwrt build directory.

I found differences in target/linux/ath79/base-files/etc/board.d/02_network

and in all files in target/linux/ar71xx/files/arch/mips/ath79/

like mach-gl-ar150.c, mach-wifi-pineapple-nano.c, mach-tl-wr940n-v4.c

in these last ones

like ar150 says ..

.......

/* disable PHY_SWAP and PHY_ADDR_SWAP bits */

ath79_setup_ar933x_phy4_switch(false, false);

................

/* register eth0 as WAN, eth1 as LAN */

ath79_init_mac(ath79_eth0_data.mac_addr, art+GL_AR150_MAC0_OFFSET, 0);

ath79_init_mac(ath79_eth1_data.mac_addr, art+GL_AR150_MAC1_OFFSET, 0);

ath79_register_mdio(0, 0x0);

ath79_register_eth(0);

ath79_register_eth(1);

......................

wifi pineapple:

...........

ath79_setup_ar933x_phy4_switch(false, false);

ath79_register_mdio(0, 0x0);

ath79_init_mac(ath79_eth0_data.mac_addr,

art + WIFI_PINEAPPLE_NANO_MAC1_OFFSET, 0);

ath79_register_eth(0);

..............................

tl-wr940n-v4.c

....................

ath79_init_mac(ath79_eth0_data.mac_addr, mac, 1);

ath79_init_mac(ath79_eth1_data.mac_addr, mac, -1);

ath79_switch_data.phy4_mii_en = 1;

ath79_register_eth(0);

ath79_register_eth(1);

......................................

then with a different SOC (ar9344 with switch AR8327) wndr4300 :

..............................................

ath79_setup_ar934x_eth_cfg(AR934X_ETH_CFG_RGMII_GMAC0);

mdiobus_register_board_info(wndr4300_mdio0_info,

ARRAY_SIZE(wndr4300_mdio0_info));

ath79_register_mdio(0, 0x0);

/* GMAC0 is connected to an AR8327N switch */

ath79_eth0_data.phy_if_mode = PHY_INTERFACE_MODE_RGMII;

ath79_eth0_data.phy_mask = BIT(0);

ath79_eth0_data.mii_bus_dev = &ath79_mdio0_device.dev;

ath79_eth0_pll_data.pll_1000 = 0x06000000;

ath79_register_eth(0);

...........................................

inside target/linux/ar71xx/base-files/etc/board.d/02_network

#!/bin/sh

Copyright (C) 2011-2015 OpenWrt.org

. /lib/functions/system.sh

. /lib/functions/uci-defaults.sh

ar71xx_setup_interfaces()

{

local board="$1"

case "$board" in

..............

wifi-pineapple-nano|\

..........

gl-ar150|\

.....................

tl-wr940n-v4|\

........................

wndr4300)

ucidef_add_switch "switch0"

"0@eth0" "1:lan:4" "2:lan:3" "3:lan:2" "4:lan:1" "5:wan"

...................................

My questions are:

1--- target/linux/ar71xx/base-files/etc/board.d/02_network

defines the UCI configuration after the network devices are already loaded in the kernel ? yes or no ?

(is it the right wording or should I say something different) ?

2--- the only references to interfaces are the ath9_register_eth(0) in the mac-XXX files

are these files responsible for the loading or configuration of the network device driver definition in the kernel ?

(is it the right wording or should I say something different) ?

3-- how if is possible (I could borrow the 4300 set up and apply it to ar150 to have the 2 ethernet sockets

(the plug on my minirouter) be handled by the built in switch ??

Remember everything started from the ar9331 datasheet claiming about the built-in switch

4-- why in the

target/linux/ar71xx/files/arch/mips/ath79/Kconfig.openwrt:

.....

config ATH79_MACH_GL_AR150

bool "GL AR150 support"

select SOC_AR933X

select ATH79_DEV_ETH

select ATH79_DEV_GPIO_BUTTONS

select ATH79_DEV_LEDS_GPIO

select ATH79_DEV_M25P80

select ATH79_DEV_USB

select ATH79_DEV_WMAC

...................

there is nothing about a switch ? I mean I could be wrong but to me sounds like

select ATH79_DEV_ETH will load a driver for ethernet controller/devices/whathever ?(right ? wrong)?

why I dont have anything related to switch ??

5-- what is the 03_network-switchX-migration in target/linux/ar71xx/etc about ?

in some lines I can read:

............................

rb-2011uas-2hnd)

migrate_switch_name "eth0" "switch0"

migrate_switch_name "eth1" "switch1"

..............................

So eth0 could refer to both a switch or a normal single physical interface ??

How I can distinguish between them ?

Hope my question are clear to You, to me they are kind out of the logic I think I its behind openwrt

but I feel I am kind far from the right track at the moment.

THanks

P.

hi

- -yes

- -yes, but they are not the only ones. they are actually, let's say, initializers of the lower-level code in dev-eth.c and similar files

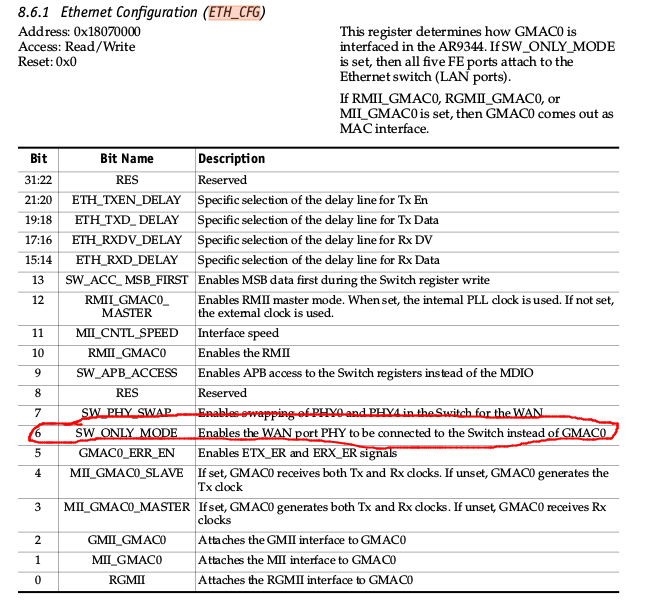

- -if the datasheet informations are not contradictory and this can work (did not check while my ar9331 devices were operational) you should look for SW_ONLY_MODE in code (it is for ar934x) and reuse it for ar933x chipset

- -because switch-related code is already in files i wrote in answer to your question 2

- -something routerboard related, i've not checked it..

regarding uci configuration, yes, eth0 could refer to whichever interface you assign it to.

when it comes to kernel driver eth0 is usually tied to gmac0 and eth1 to gmac1 (this one shows link speed 1000Mbps in logs)

Hi Psyborg,

found online the ar9344 soc datasheet quite impressive ar7100.pdf is 112pages; ar9331.pdf is 320pages and ar9344.pdf is466pages.

And here the SW_ONLY_MODE part.

Talking about reusing it for ar933x chipset bring me to the:

Atheros AR71XX/AR724X/AR913X SoC register definitions in

openwrt/target/linux/ar71xx/image/lzma-loader/src/ar71xx_regs.h

where I find:

........................................

/*

- AR933X GMAC interface

*/

#define AR933X_GMAC_REG_ETH_CFG 0x00

#define AR933X_ETH_CFG_RGMII_GE0 BIT(0)

#define AR933X_ETH_CFG_MII_GE0 BIT(1)

#define AR933X_ETH_CFG_GMII_GE0 BIT(2)

#define AR933X_ETH_CFG_MII_GE0_MASTER BIT(3)

#define AR933X_ETH_CFG_MII_GE0_SLAVE BIT(4)

#define AR933X_ETH_CFG_MII_GE0_ERR_EN BIT(5)

#define AR933X_ETH_CFG_SW_PHY_SWAP BIT(7)

#define AR933X_ETH_CFG_SW_PHY_ADDR_SWAP BIT(8)

#define AR933X_ETH_CFG_RMII_GE0 BIT(9)

#define AR933X_ETH_CFG_RMII_GE0_SPD_10 0

#define AR933X_ETH_CFG_RMII_GE0_SPD_100 BIT(10)

/*

- AR934X GMAC Interface

*/

#define AR934X_GMAC_REG_ETH_CFG 0x00

#define AR934X_ETH_CFG_RGMII_GMAC0 BIT(0)

#define AR934X_ETH_CFG_MII_GMAC0 BIT(1)

#define AR934X_ETH_CFG_GMII_GMAC0 BIT(2)

#define AR934X_ETH_CFG_MII_GMAC0_MASTER BIT(3)

#define AR934X_ETH_CFG_MII_GMAC0_SLAVE BIT(4)

#define AR934X_ETH_CFG_MII_GMAC0_ERR_EN BIT(5)

#define AR934X_ETH_CFG_SW_ONLY_MODE BIT(6)

#define AR934X_ETH_CFG_SW_PHY_SWAP BIT(7)

#define AR934X_ETH_CFG_SW_APB_ACCESS BIT(9)

#define AR934X_ETH_CFG_RMII_GMAC0 BIT(10)

#define AR933X_ETH_CFG_MII_CNTL_SPEED BIT(11)

#define AR934X_ETH_CFG_RMII_GMAC0_MASTER BIT(12)

#define AR933X_ETH_CFG_SW_ACC_MSB_FIRST BIT(13)

................................................

Now I'll have to find out what the lzma-loader is but first of all a question for You:

is the ar71xx_regs.h file patchable or I just have to add a

#define AR934X_ETH_CFG_SW_ONLY_MODE BIT(6) line to ar93x1 GMAC interface block

inside the ar71xx_regs.h file? That's because I wasn' t able to find the file in the build_dir as per openwrt

patching instructions: https://openwrt.org/docs/guide-developer/build-system/use-patches-with-buildsystem.

In the meanwhile ill work on the other occurencies of SW_ONLY_MODE inside openwrt

hopefully I'll found a board that uses this switch only mode inside the target/ar71xx directory

Thanks again

Bests

P.

look for airgateway pro in mach-ubnt-xm, /* GMAC0 is left unused in this configuration */

ar9331 datasheet shows bit(6) as reserved and RO. unless it is some other bit you could try just using ath79_setup_ar934x_eth_cfg(AR934X_ETH_CFG_SW_ONLY_MODE);

good luck

sorry I meant #define AR933X_ETH_CFG_SW_ONLY_MODE BIT(6) line to ar933x GMAC interface block

Hi everybody, hoping that Psyborg is listening.

I am going mad trying to figure out how openwrt makefile proceds through the building tree.

Questions

- Does Buildroot 'make graph-depends' works on openwrt ?

I tried make graph-depends but no success.

Still working on ar150 soc ar9331 and built in switch behaviour

(funny note my kernel says SoC: Atheros AR9330 rev 1 but on the actual chip I can read ar9331)

-

what is the difference between openwrt/target/linux/ar71xx

and openwrt/target/linux/ath79 ?

Are the two directory related meaning while building for my

ar150 device makefile uses pieces of both the directories or only the one I select

with make menuconfig, (that being ar71xx) ? -

surfed between mach-gl-ar150.c , dev-eth.h dev-eth.c ar71xx_regs.h ag71xx_platform.h

trying to figure out differences between ar933x and ar934x, remember I am starting from

AR934X_ETH_CFG_SW_ONLY_MODE. Is there some documentation that explains at list

the relation between these files during building process ? -

I noticed, I wish, I had noticed earlier in ar71xx_regs.h:

*

* AR933X GMAC interface

*/

#define AR933X_GMAC_REG_ETH_CFG 0x00

#define AR933X_ETH_CFG_RGMII_GE0 BIT(0)

#define AR933X_ETH_CFG_MII_GE0 BIT(1)

#define AR933X_ETH_CFG_GMII_GE0 BIT(2)

#define AR933X_ETH_CFG_MII_GE0_MASTER BIT(3)

#define AR933X_ETH_CFG_MII_GE0_SLAVE BIT(4)

#define AR933X_ETH_CFG_MII_GE0_ERR_EN BIT(5)

#define AR933X_ETH_CFG_SW_ONLY_MODE BIT(6) I added this line to copy mach-ubnt-xm behaviour

#define AR933X_ETH_CFG_SW_PHY_SWAP BIT(7)

#define AR933X_ETH_CFG_SW_PHY_ADDR_SWAP BIT(8)

#define AR933X_ETH_CFG_RMII_GE0 BIT(9)

#define AR933X_ETH_CFG_RMII_GE0_SPD_10 0

#define AR933X_ETH_CFG_RMII_GE0_SPD_100 BIT(10)

/*

* AR934X GMAC Interface

*/

#define AR934X_GMAC_REG_ETH_CFG 0x00

#define AR934X_ETH_CFG_RGMII_GMAC0 BIT(0)

#define AR934X_ETH_CFG_MII_GMAC0 BIT(1)

#define AR934X_ETH_CFG_GMII_GMAC0 BIT(2)

#define AR934X_ETH_CFG_MII_GMAC0_MASTER BIT(3)

#define AR934X_ETH_CFG_MII_GMAC0_SLAVE BIT(4)

#define AR934X_ETH_CFG_MII_GMAC0_ERR_EN BIT(5)

#define AR934X_ETH_CFG_SW_ONLY_MODE BIT(6)

#define AR934X_ETH_CFG_SW_PHY_SWAP BIT(7)

#define AR934X_ETH_CFG_SW_APB_ACCESS BIT(9)

#define AR934X_ETH_CFG_RMII_GMAC0 BIT(10)

#define AR933X_ETH_CFG_MII_CNTL_SPEED BIT(11)

#define AR934X_ETH_CFG_RMII_GMAC0_MASTER BIT(12)

#define AR933X_ETH_CFG_SW_ACC_MSB_FIRST BIT(13)

that ar933x defines GE0 while ar9334 defines GMAC0.

Can I just consider them the same and copy ar934x GMAC0 pieces of code

changing them with GE0 ???

- Right now I'm just trying to copy pieces of code between the two mach different files

(mach-gl-ar-150.c and mach-ubnt-xm.c) but I spend a lot time waiting for

results of compiling, always getting errors of course. I am using the bare minimum

selected ar71xx and gl-ar150 no other stuff (packages, modules etc).

Is there a way to shorten the building time ?

Thanks any help will be appreciate

Bests

P.

Hi sorry again,

still about the

#define AR933X_ETH_CFG_SW_ONLY_MODE BIT(6)

I am stuck at:

# make target/linux/{clean,prepare} V=s QUILT=1

# cd build_dir/target-mips_24kc_musl/linux-ar71xx_generic/linux-4.9.124/arch/mips/include/asm/mach-ath79

# quilt series

# quilt push platform/601-MIPS-ath79-add-more-register-defines.patch

.....................

.....................

Applying patch platform/105-spi-spi-ath79-use-gpio_set_value_cansleep-for-GPIO-c.patch

patching file drivers/spi/spi-ath79.c

Applying patch platform/106-02-MIPS-ath79-do-AR724x-PCIe-root-complex-init.patch

patching file arch/mips/include/asm/mach-ath79/ar71xx_regs.h

Hunk #1 FAILED at 169.

1 out of 1 hunk FAILED -- rejects in file arch/mips/include/asm/mach-ath79/ar71xx_regs.h

patching file arch/mips/pci/pci-ar724x.c

Patch platform/106-02-MIPS-ath79-do-AR724x-PCIe-root-complex-init.patch does not apply (enforce with -f)

kk@kk-WC:~/Documents/openwrt/build_dir/target-mips_24kc_musl/linux-ar71xx_generic/linux-4.9.124/arch/mips/include/asm/mach-ath79$

.......................

I had a look at

openwrt/target/linux/ar71xx/patches-4.9/106-02-MIPS-ath79-do-AR724x-PCIe-root-complex-init.patch

--- a/arch/mips/include/asm/mach-ath79/ar71xx_regs.h

+++ b/arch/mips/include/asm/mach-ath79/ar71xx_regs.h

@@ -169,6 +169,9 @@

#define AR724X_PLL_REG_CPU_CONFIG 0x00

#define AR724X_PLL_REG_PCIE_CONFIG 0x10

+#define AR724X_PLL_REG_PCIE_CONFIG_PPL_BYPASS BIT(16)

+#define AR724X_PLL_REG_PCIE_CONFIG_PPL_RESET BIT(25)

+

#define AR724X_PLL_FB_SHIFT 0

#define AR724X_PLL_FB_MASK 0x3ff

#define AR724X_PLL_REF_DIV_SHIFT 10

--- a/arch/mips/pci/pci-ar724x.c

+++ b/arch/mips/pci/pci-ar724x.c

@@ -12,14 +12,18 @@

#include <linux/irq.h>

#include <linux/pci.h>

#include <linux/init.h>

+#include <linux/delay.h>

...............................

a patch file pointing to two differents files ? I know I should study more but I first heard about patches

about one month ago !!

Does anybody have a clue how to get over this to finally having a chance to modify my

601-MIPS-ath79-add-more-register-defines.patch ?

Thanks a lot

Bests

P.

Hi,

my big mistake was working with trunk

remade the patching after downloding the right openwrt last stable release: v18.06.1 (is it right?)

Worked fine.

EDITED: working on trunk with target system as Atheros ATH79 too

Bests

P.

Hi to whoever is listening:

recap so far:

normal gl-ar150 soc ar9330/9331, setup openwrt 18.06.1 4.9 kernel :

mydiffconfig:

CONFIG_TARGET_ar71xx=y

CONFIG_TARGET_ar71xx_generic=y

CONFIG_TARGET_ar71xx_generic_DEVICE_gl-ar150=y

kernel boot-up:

[ 0.911395] libphy: Fixed MDIO Bus: probed

[ 0.934519] libphy: ag71xx_mdio: probed

[ 1.564501] ag71xx ag71xx.0: connected to PHY at ag71xx-mdio.1:04 [uid=004dd041, driver=Generic PHY]

[ 1.573311] eth0: Atheros AG71xx at 0xb9000000, irq 4, mode:MII

[ 2.204269] ag71xx-mdio.1: Found an AR7240/AR9330 built-in switch

[ 2.246422] eth1: Atheros AG71xx at 0xba000000, irq 5, mode:GMII

devices loaded

root@OpenWrt:/# ls -l /sys/class/net

lrwxrwxrwx 1 root root 0 Aug 16 07:51 br-lan -> ../../devices/virtual/net/br-lan

lrwxrwxrwx 1 root root 0 Jan 1 1970 eth0 -> ../../devices/platform/ag71xx.0/net/eth0

lrwxrwxrwx 1 root root 0 Jan 1 1970 eth1 -> ../../devices/platform/ag71xx.1/net/eth1

lrwxrwxrwx 1 root root 0 Jan 1 1970 lo -> ../../devices/virtual/net/lo

lrwxrwxrwx 1 root root 0 Aug 16 08:01 wlan0 -> ../../devices/platform/ar933x_wmac/net/wlan0

swconfig output

root@OpenWrt:/# swconfig dev eth1 show

Global attributes:

enable_vlan: 0

mirror_monitor_port: 15

Port 0:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:0 link:up speed:1000baseT full-duplex txflow rxflow

Port 1:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:1 link:up speed:100baseT full-duplex auto

Port 2:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:2 link:down

Port 3:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:3 link:down

Port 4:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:4 link:down

VLAN 0:

vid: 0

ports: 0 1 2 3 4

modified by me trying to copy airgateway pro in mach-ubnt-xm.c setup

myfdiffconfig is the same

kernel boot-up:

[ 0.768925] libphy: Fixed MDIO Bus: probed

[ 0.794232] libphy: ag71xx_mdio: probed

[ 1.425525] ag71xx-mdio.1: Found an AR7240/AR9330 built-in switch

[ 1.467726] eth0: Atheros AG71xx at 0xba000000, irq 5, mode:GMII

devices loaded

root@OpenWrt:/# ls -l sys/class/net/

lrwxrwxrwx 1 root root 0 Jan 1 1970 eth0 -> ../../devices/platform/ag71xx.1/net/eth0

lrwxrwxrwx 1 root root 0 Jan 1 1970 lo -> ../../devices/virtual/net/lo

lrwxrwxrwx 1 root root 0 Aug 16 07:54 wlan0 -> ../../devices/platform/ar933x_wmac/net/wlan0

swconfig output

root@OpenWrt:/# swconfig dev eth0 show

Global attributes:

enable_vlan: 1

mirror_monitor_port: 15

Port 0:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:0 link:up speed:1000baseT full-duplex txflow rxflow

Port 1:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:1 link:up speed:100baseT full-duplex auto

Port 2:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:2 link:down

Port 3:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:3 link:down

Port 4:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:4 link:down

VLAN 0:

vid: 0

ports: 0 1 2 3 4

Its like I lost a PHY in between the two set ups, see kernel boot logs, and following airgateway-pro setup its

like I am using mdio1 to connect gemac0 to the router and the speed is not GMII1000 nbt seems like 100 !!?? The router seems to work fine

in fact eth0 is displayed as 1000

[ 783.878291] IPv6: ADDRCONF(NETDEV_CHANGE): wlan0: link becomes ready

[ 783.883478] br-lan: port 1(wlan0) entered blocking state

[ 783.888606] br-lan: port 1(wlan0) entered forwarding state

[ 783.910666] IPv6: ADDRCONF(NETDEV_CHANGE): br-lan: link becomes ready

root@OpenWrt:/# [ 832.624377] eth0: link down

[ 838.235268] eth0: link up (1000Mbps/Full duplex)

I can use both serial or ssh throught eth0 but its like I cannot get the second rj45 socket to work.

I tried different switch config options in etc/config/network but I cannot get them to work.

What Am I missing ??

I noticed that openwrt/target/linux/ar71xx/files/drivers/net/ethernet/atheros/ag71xx/ag71xx_ar7240.c

contains references to ar934x but I wasnt able to figure out how to trigger them for my soc9330.

could be this one the problem or should I try some different special

etc/config/network/ switch config lines or some particular uci setup in etc/board.d/02_network ?

when I connect to router through eth0 (lan) dmesg gives:

[ 857.471148] device eth0 entered promiscuous mode

[ 857.475277] br-lan: port 2(eth0) entered blocking state

[ 857.480299] br-lan: port 2(eth0) entered forwarding state

but swconfig dev eth0 show gives:

root@OpenWrt:/# swconfig dev eth0 show

Global attributes:

enable_vlan: 0

mirror_monitor_port: 15

Port 0:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:0 link:up speed:1000baseT full-duplex txflow rxflow

Port 1:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:1 link:up speed:100baseT full-duplex auto

Port 2:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:2 link:down

ok port2 in br-lan refers to the br-lan itself connectiong to router by wifi gives

[ 1983.439870] device wlan0 entered promiscuous mode

[ 1984.281387] IPv6: ADDRCONF(NETDEV_CHANGE): wlan0: link becomes ready

[ 1984.286683] br-lan: port 1(wlan0) entered blocking state

[ 1984.291605] br-lan: port 1(wlan0) entered forwarding state

So what about the switch and his ports ?? Any insight appreciated.

Updates

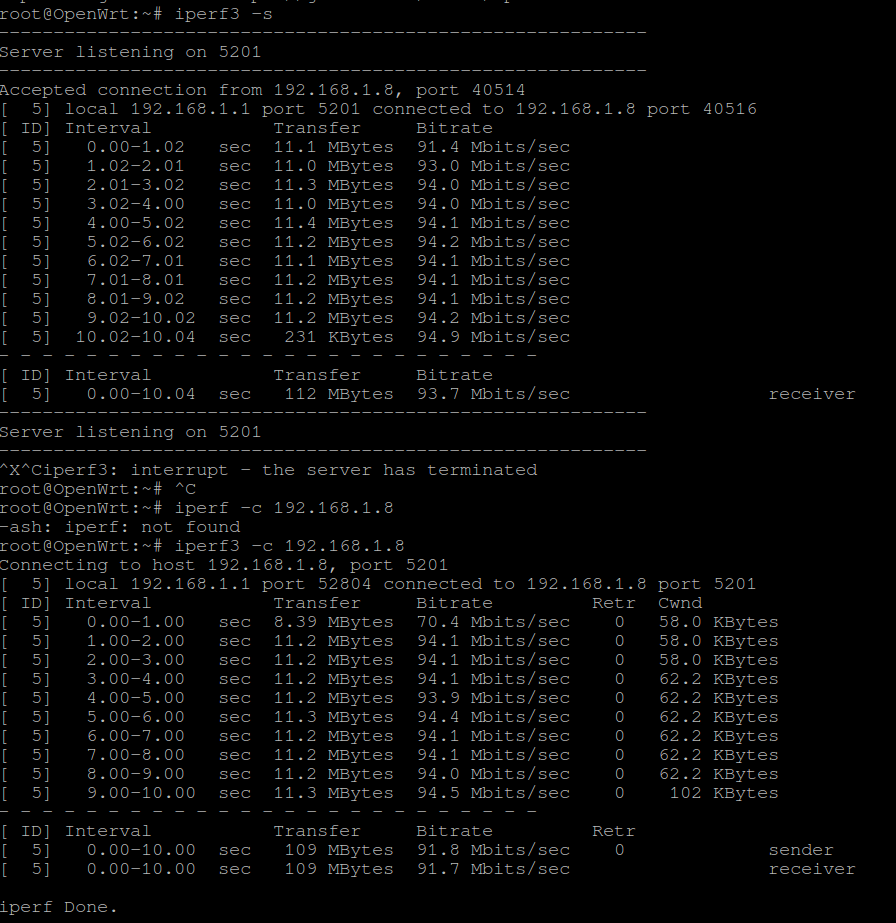

using iperf3 I verified that the actual spped of my rj45 plug is mii

Making some really random change to

openwrt/target/lunix/files/drivers/net/ethernet/atheros/ag71xx/ag71xx_ar7240.c-

I ended up having

lrwxrwxrwx 1 root root 0 Aug 16 08:15 br-lan -> ../../devices/virtual/net/br-lan

lrwxrwxrwx 1 root root 0 Jan 1 1970 eth0 -> ../../devices/platform/ag71xx.1/net/eth0

lrwxrwxrwx 1 root root 0 Jan 1 1970 lo -> ../../devices/virtual/net/lo

lrwxrwxrwx 1 root root 0 Aug 16 08:15 wlan0 -> ../../devices/platform/ar933x_wmac/net/wlan0

but when attacching cable to second rj45 plug I get

root@OpenWrt:/# root@OpenWrt:/# swconfig dev eth0 show

Global attributes:

enable_vlan: 0

mirror_monitor_port: 15

Port 0:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:0 link:up speed:1000baseT full-duplex txflow rxflow

Port 1:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:1 link:up speed:100baseT full-duplex auto

Port 2:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:2 link:down

Port 3:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:3 link:down

Port 4:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:4 link:down

Port 5:

enable_mirror_rx: 0

enable_mirror_tx: 0

pvid: 0

link: port:5 link:up speed:100baseT full-duplex auto

VLAN 0:

vid: 0

ports: 0 1 2 3 4 5

Everything seems to me out of synch with the openwrt wiki and everything above ? any insight ?

Its like I got a bonus 5 port on the switch that at this point I don't know if its a real one or just software ?

I'll try to see if I can get the swconfig tool to set the two interfaces and have the router working as a dumb AP as per my initial idea.

Updates

modified a bit more the openwrt/target/lunix/files/drivers/net/ethernet/atheros/ag71xx/ag71xx_ar7240.c

strange that having in my openwrt build a premade etc/config/wireless configuration file

was giving me strange boot up problems, a new thing to investigate

I am not sure about ethernet working right now. So far I can reach the router by wifi

but what is strange to me is

root@OpenWrt:/# dmesg | grep eth0

[ 1.478990] eth0: Atheros AG71xx at 0xba000000, irq 5, mode:GMII

[ 4.948986] IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready

[ 15.008374] IPv6: ADDRCONF(NETDEV_UP): eth0: link is not ready

[ 22.020986] br-lan: port 1(eth0) entered blocking state

[ 22.024775] br-lan: port 1(eth0) entered disabled state

[ 22.030708] device eth0 entered promiscuous mode

[ 1529.486406] eth0: link up (1000Mbps/Full duplex)

[ 1529.489652] br-lan: port 1(eth0) entered blocking state

[ 1529.494798] br-lan: port 1(eth0) entered forwarding state

root@OpenWrt:/# dmesg | grep wlan0

[ 26.249954] IPv6: ADDRCONF(NETDEV_UP): wlan0: link is not ready

[ 26.271149] br-lan: port 2(wlan0) entered blocking state

[ 26.275187] br-lan: port 2(wlan0) entered disabled state

[ 26.280960] device wlan0 entered promiscuous mode

[ 27.595191] IPv6: ADDRCONF(NETDEV_CHANGE): wlan0: link becomes ready

[ 27.600466] br-lan: port 2(wlan0) entered blocking state

[ 27.605551] br-lan: port 2(wlan0) entered forwarding state

[ 1007.561313] br-lan: port 2(wlan0) entered disabled state

[ 4366.679637] IPv6: ADDRCONF(NETDEV_UP): wlan0: link is not ready

[ 22.020986] br-lan: port 1(eth0) entered blocking state

[ 26.275187] br-lan: port 2(wlan0) entered disabled state

I just wanted to mirror eth0 plug to second available (not sure yet !!) Rj45 plug

Now I have strange ports on bridged interface !!

Let's see what happen next.

In the meanwhile if aybody working with ar934x platform could/would share his experience I would really appreciate it

I think I'll mark this topic as closed. The rewiring seems to work and I am able to mirror traffic

solution is here: Swconfig versus etc/config/network

2 Questions remain open

1st Swconfig versus etc/config/network

its about how to have the righ UCI and Luci config for this setting

2nd [Solved] Router-set-up advertising

its about how to set up router advertising or enabling answer to arp request by this

configuration SOLVED was bad switch configuration file

Both question have their own topic open at the moment

Help is needed

Thanks to everyone

This topic was automatically closed 10 days after the last reply. New replies are no longer allowed.