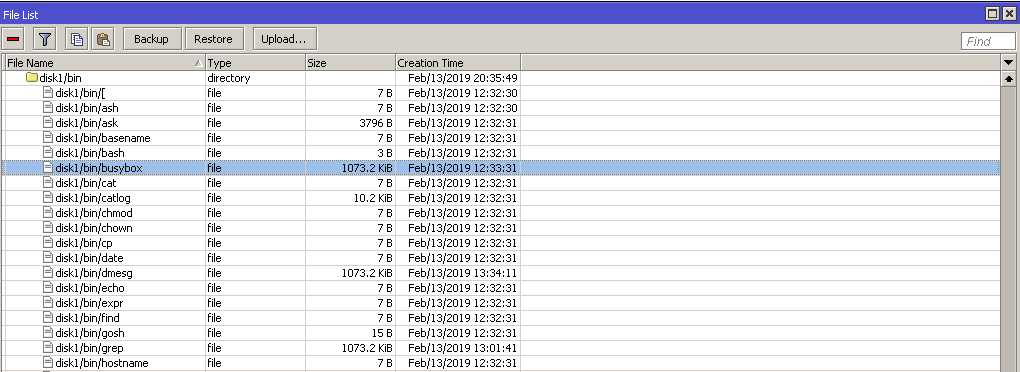

Whats about winbox? Can you show something like this:

After using MC it works.

I get dropped to root shell and BusyBox 1.0 which MT uses.

GPIOs are ones that we already knew.

# cat /sys/kernel/debug/gpio

GPIOs 0-151, msmgpio.3:

gpio-0 (power-led ) out hi

gpio-1 (led2 ) out lo

gpio-2 (led3 ) out lo

gpio-3 (user-led ) out lo

gpio-4 (led4 ) out lo

gpio-5 (led5 ) out lo

gpio-58 (led1 ) out lo

gpio-63 (button ) in hi

gpio-66 (80000.qcom,pcie ) out lo

Try to use this kernel module:

Upload it to /tmp and then do insmod ./test_m.ko

After that see dmesg -c for results.

For example on RB450Gx4 I see this:

My nss_read_phy_reg(0xbd000000, 0x18, 0x1), 0x7f61b4f4

My nss_read_phy_reg(0xbd000000, 0x19, 0x1), 0x7f61b4f4

My nss_read_phy_reg(0xbd000000, 0x1a, 0x1), 0x7f61b4f4

My nss_read_phy_reg(0xbd000000, 0x1b, 0x1), 0x7f61b4f4

My nss_read_phy_reg(0xbd000000, 0x1c, 0x1), 0x7f61b4f4

My nss_read_phy_reg(0xbd000000, 0x18, 0x1), 0x7f61b4f4

My nss_read_phy_reg(0xbd000000, 0x19, 0x1), 0x7f61b4f4

My nss_read_phy_reg(0xbd000000, 0x1a, 0x1), 0x7f61b4f4

My nss_read_phy_reg(0xbd000000, 0x1b, 0x1), 0x7f61b4f4

My nss_read_phy_reg(0xbd000000, 0x1c, 0x1), 0x7f61b4f4

Ok, here we go

My nss_read_phy_reg(0x8e240000, 0x0, 0x1), 0x7f6154f4

My nss_read_phy_reg(0x8e240000, 0x0, 0x1), 0x7f6154f4

My nss_read_phy_reg(0x8e240000, 0x0, 0x1), 0x7f6154f4

My nss_read_phy_reg(0x8e240000, 0x0, 0x1), 0x7f6154f4

My nss_read_phy_reg(0x8e240000, 0x0, 0x1), 0x7f6154f4

My nss_read_phy_reg(0x8e240000, 0x0, 0x1), 0x7f6154f4

My nss_read_phy_reg(0x8e240000, 0x0, 0x1), 0x7f6154f4

My nss_read_phy_reg(0x8e240000, 0x0, 0x1), 0x7f6154f4

My nss_read_phy_reg(0x8e240000, 0x0, 0x1), 0x7f6154f4

According to this there is no offset at all.

But address its reading from is completely different.

Its like its reading from AR8035 directly instead of internal MDIO

No. The address 0x8e240000 is just an internal pointer to struct mii_dev *dev.

All we need here is mii_id := 0x0 and reg := 0x1.

This is a survey of the port state(once per second).

Then it means that it should be detected at default setting but no MDIO is detected at all.

Try to use this new test_m build.

I add a filter IF for survey of the port state.

Try to enable/disable ether1 in RouterOS and show dmesg -c results.

Well, I cant really disable it as this device only has one port so disabling it means I have no way of retrieveng dmesg

You can disable/enable it via UART Console and then do telnet and see a dmesg results.

Well I cant since UART stops after this:

RouterBOOT booter 6.44

RBLHGG-60ad

CPU frequency: 716 MHz

Memory size: 256 MiB

Storage size: 16 MiB

Press any key within 2 seconds to enter setup..

trying dhcp protocol... OK

resolved mac address C4:93:00:0F:30:DA

Gateway: 192.168.1.1

transfer started ............. transfer ok, time=1.16s

setting up elf image... OK

jumping to kernel code

Starting...

Launching telnetd

Starting services...

There is no interactive shell

This is what dmesg captured before locking myself out with disabling port

switch_port_mdio_write: victim base = 0x7f054000

switch_port_mdio_write: pip = 0x7f61a074

switch_port_mdio_write: orig 0xe92d4008, 0xe590097c, 0xe590c058

switch_port_mdio_write: new 0xe30a9074, 0xe3479f61, 0xe1a0f009

switch_port_mdio_read: victim base = 0x7f0589b0

switch_port_mdio_read: pip = 0x7f61a154

switch_port_mdio_read: orig 0xe92d40f8, 0xe1a04000, 0xe590097c

switch_port_mdio_read: new 0xe30a9154, 0xe3479f61, 0xe1a0f009

This is not matter info.

Well after factory resetting now for some reason UART started working in RouterOS too.

Gotta jailbreak it again and then I can use UART to disable/enable

I this is was disabled in previous setup.

Most likely as default config was generated while UART was disabled

When we work on Rb450Gx4 i wrote a test mdio kernel module for OpenWRT:

It result for RB450Gx4:

[ 564.775459] ipq_mdio reg0 = 0x150ff

[ 564.775497] ipq_mdio reg1 = 0x1c11

[ 564.777758] ipq_mdio reg2 = 0x8000

[ 564.781273] ipq_mdio reg3 = 0x10

[ 564.784616] ipq_mdio reg3 = 0x0

[ 564.788182] PHY ID1: 0x4d

[ 564.791096] PHY ID2: 0xd0b1

Try to play with this module.

Edit a cross compile path in arm.mk and do make

Ok,

here is couple of dmesg -c s after disable/enable

It is very strange that only nss_read_phy_reg is called and only for reading the status of the port.

Must be other that 0x1 registers and write ops too!

Hm, I disabled 60GHz card as it was spamming the log.

And I left port disabled for couple of minutes and then enabled it

/flash/rw/tmp # dmesg -c

device eth0 left promiscuous mode

packet_hook: inject on nonexisting dev: 9

eth0: set isolation from 1 to 0

switch0-eth0: set switched 0 20

device eth0 entered promiscuous mode

eth0: set isolation from 0 to 1

switch0-eth0: set switched 0 20

On RB450Gx4 when I disable/enable port5:

My nss_write_phy_reg(0xbe7a0000, 0x1c, 0x0, 0x8000), 0x7f61b46c

My nss_read_phy_reg(0xbe7a0000, 0x1c, 0x0), 0x7f61b4f4

My nss_write_phy_reg(0xbe7a0000, 0x1c, 0x0, 0x1200), 0x7f61b46c

My nss_read_phy_reg(0xbe7a0000, 0x1c, 0x2), 0x7f61b4f4

My nss_read_phy_reg(0xbe7a0000, 0x1c, 0x3), 0x7f61b4f4

My nss_read_phy_reg(0xbe7a0000, 0x1c, 0x0), 0x7f61b4f4

My nss_write_phy_reg(0xbe7a0000, 0x1c, 0x0, 0x9000), 0x7f61b46c

My nss_read_phy_reg(0xbe7a0000, 0x1c, 0x0), 0x7f61b4f4

My nss_write_phy_reg(0xbe7a0000, 0x1c, 0x0, 0x1200), 0x7f61b46c

My nss_read_phy_reg(0xbe7a0000, 0x1c, 0x2), 0x7f61b4f4

My nss_read_phy_reg(0xbe7a0000, 0x1c, 0x3), 0x7f61b4f4

My nss_read_phy_reg(0xbe7a0000, 0x1c, 0x4), 0x7f61b4f4

My nss_read_phy_reg(0xbe7a0000, 0x1c, 0x9), 0x7f61b4f4

My nss_read_phy_reg(0xbe7a0000, 0x1c, 0x0), 0x7f61b4f4

My nss_write_phy_reg(0xbe7a0000, 0x1c, 0x0, 0x1200), 0x7f61b46c

So It used mii_id 0x1c and registers 0x0, 0x2, 0x3, 0x4, 0x9.