I got the serial port working and Got bunch of boot logs

===================================================================

MT7621 stage1 code Mar 12 2015 14:42:52 (ASIC)

CPU=50000000 HZ BUS=16666666 HZ

==================================================================

Change MPLL source from XTAL to CR...

do MEMPLL setting..

MEMPLL Config : 0x11100000

3PLL mode + External loopback

=== XTAL-40Mhz === DDR-1200Mhz ===

PLL3 FB_DL: 0xe, 1/0 = 617/407 39000000

PLL4 FB_DL: 0x14, 1/0 = 713/311 51000000

PLL2 FB_DL: 0x19, 1/0 = 643/381 65000000

do DDR setting..[00320381]

Apply DDR3 Setting...(use customer AC)

0 8 16 24 32 40 48 56 64 72 80 88 96 104 112 120

--------------------------------------------------------------------------------

0000:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0001:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0002:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0003:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0004:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0005:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0006:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0007:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0008:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0009:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000A:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000B:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000C:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000D:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

000E:| 0 0 0 0 0 0 0 0 0 0 1 1 1 1 1 1

000F:| 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 0

0010:| 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 0

0011:| 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0

0012:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0013:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0014:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0015:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0016:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0017:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0018:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0019:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001A:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001B:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001C:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001D:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001E:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

001F:| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

DRAMC_DQSCTL1[0e0]=14000000

DRAMC_DQSGCTL[124]=80000000

rank 0 coarse = 16

rank 0 fine = 40

B:| 0 0 0 0 0 0 0 0 1 1 1 0 0 0 0 0

opt_dle value:9

DRAMC_DDR2CTL[07c]=C287221D

DRAMC_PADCTL4[0e4]=000022B3

DRAMC_DQIDLY1[210]=0F0D0F0F

DRAMC_DQIDLY2[214]=0C0D0E0D

DRAMC_DQIDLY3[218]=0D0D0B0C

DRAMC_DQIDLY4[21c]=0E0A0F0B

DRAMC_R0DELDLY[018]=00001D1F

==================================================================

RX DQS perbit delay software calibration

==================================================================

1.0-15 bit dq delay value

==================================================================

bit| 0 1 2 3 4 5 6 7 8 9

--------------------------------------

0 | 13 12 13 14 11 11 13 9 11 10

10 | 13 13 11 15 10 14

--------------------------------------

==================================================================

2.dqs window

x=pass dqs delay value (min~max)center

y=0-7bit DQ of every group

input delay:DQS0 =31 DQS1 = 29

==================================================================

bit DQS0 bit DQS1

0 (1~55)28 8 (1~56)28

1 (1~56)28 9 (1~56)28

2 (2~60)31 10 (1~58)29

3 (0~59)29 11 (1~57)29

4 (1~57)29 12 (1~58)29

5 (1~56)28 13 (1~57)29

6 (1~61)31 14 (1~57)29

7 (1~56)28 15 (1~57)29

==================================================================

3.dq delay value last

==================================================================

bit| 0 1 2 3 4 5 6 7 8 9

--------------------------------------

0 | 15 15 13 15 13 14 13 12 12 11

10 | 13 13 11 15 10 14

==================================================================

==================================================================

TX perbyte calibration

==================================================================

DQS loop = 15, cmp_err_1 = ffff0000

dqs_perbyte_dly.last_dqsdly_pass[0]=15, finish count=1

dqs_perbyte_dly.last_dqsdly_pass[1]=15, finish count=2

DQ loop=15, cmp_err_1 = ffff03fe

DQ loop=14, cmp_err_1 = ffff01a2

DQ loop=13, cmp_err_1 = ffff0182

DQ loop=12, cmp_err_1 = ffff0080

dqs_perbyte_dly.last_dqdly_pass[1]=12, finish count=1

DQ loop=11, cmp_err_1 = ffff0080

DQ loop=10, cmp_err_1 = ffff0000

dqs_perbyte_dly.last_dqdly_pass[0]=10, finish count=2

byte:0, (DQS,DQ)=(a,8)

byte:1, (DQS,DQ)=(9,8)

DRAMC_DQODLY1[200]=88888888

DRAMC_DQODLY2[204]=88888888

20,data:9a

[EMI] DRAMC calibration passed

===================================================================

MT7621 stage1 code done

CPU=50000000 HZ BUS=16666666 HZ

===================================================================

(Dec 17 2019 - 11:14:25)

Board: Ralink APSoC DRAM: 128 MB

relocate_code Pointer at: 87f94000

Config XHCI 40M PLL

Allocate 16 byte aligned buffer: 87fc8af0

Enable NFI Clock

# MTK NAND # : Use HW ECC

NAND ID [C8 D1 80 95 40]

Device found in MTK table, ID: c8d1, EXT_ID: 809540

Support this Device in MTK table! c8d1

select_chip

[NAND]select ecc bit:4, sparesize :64 spare_per_sector=16

Signature matched and data read!

load_fact_bbt success 1023

load fact bbt success

[mtk_nand] probe successfully!

mtd->writesize=2048 mtd->oobsize=64, mtd->erasesize=131072 devinfo.iowidth=8

.*** Warning - bad CRC, using default environment

============================================

Ralink UBoot Version: 5.0.0.0

--------------------------------------------

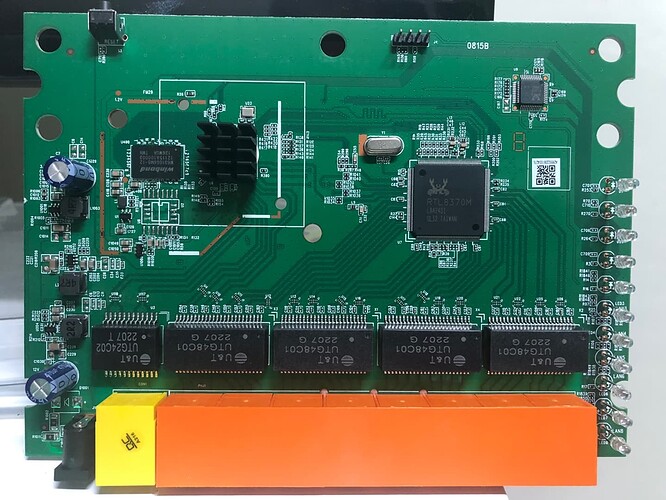

ASIC MT7621A DualCore (MAC to MT7530 Mode)

DRAM_CONF_FROM: Auto-Detection

DRAM_TYPE: DDR3

DRAM bus: 16 bit

Xtal Mode=3 OCP Ratio=1/3

Flash component: NAND Flash

Date:Dec 17 2019 Time:11:14:25

============================================

icache: sets:256, ways:4, linesz:32 ,total:32768

dcache: sets:256, ways:4, linesz:32 ,total:32768

##### The CPU freq = 880 MHZ ####

estimate memory size =128 Mbytes

#Reset_MT7530

set LAN/WAN WLLLL

Disable WAN port....

cur reg0 = 00001040

new reg0 = 00001840

Please choose the operation: (t:tftp server/b(boot now)/f(flash test)/u(upgrade boot))

default: b 0

MAC : 00:00:aa:bb:cc:dd

Alias :

3: System Boot system code via Flash.

## Booting image at bc140000 ...

Image Name: t5008

Image Type: MIPS Linux Kernel Image (lzma compressed)

Data Size: 10045332 Bytes = 9.6 MB

Load Address: 81001000

Entry Point: 8142d5a0

.......................................................................................................................................................... Verifying Checksum ... OK

Uncompressing Kernel Image ... OK

No initrd

## Transferring control to Linux (at address 8142d5a0) ...

## Giving linux memsize in MB, 128

Starting kernel ...

LINUX started...

THIS IS ASIC

SDK 5.0.S.0

[ 0.000000] Linux version 3.10.108 (scchoi@51e0cb060570) (gcc version 4.6.3 (Buildroot 2012.11.1) ) #143 SMP Mon May 2 09:48:38 KST 2022

[ 0.000000]

[ 0.000000] The CPU feqenuce set to 880 MHz

[ 0.000000] GCMP present

[ 0.000000] CPU0 revision is: 0001992f (MIPS 1004Kc)

[ 0.000000] Software DMA cache coherency

[ 0.000000] Determined physical RAM map:

[ 0.000000] memory: 08000000 @ 00000000 (usable)

[ 0.000000] Zone ranges:

[ 0.000000] DMA [mem 0x00000000-0x00ffffff]

[ 0.000000] Normal [mem 0x01000000-0x07ffffff]

[ 0.000000] Movable zone start for each node

[ 0.000000] Early memory node ranges

[ 0.000000] node 0: [mem 0x00000000-0x07ffffff]

[ 0.000000] Detected 3 available secondary CPU(s)

[ 0.000000] Primary instruction cache 32kB, 4-way, VIPT, linesize 32 bytes.

[ 0.000000] Primary data cache 32kB, 4-way, PIPT, no aliases, linesize 32 bytes

[ 0.000000] MIPS secondary cache 256kB, 8-way, linesize 32 bytes.

[ 0.000000] PERCPU: Embedded 7 pages/cpu @8170f000 s6336 r8192 d14144 u32768

[ 0.000000] Built 1 zonelists in Zone order, mobility grouping on. Total pages: 32512

[ 0.000000] Kernel command line: console=ttyS1,57600n8 root=/dev/mtdblock5

[ 0.000000] PID hash table entries: 512 (order: -1, 2048 bytes)

[ 0.000000] Dentry cache hash table entries: 16384 (order: 4, 65536 bytes)

[ 0.000000] Inode-cache hash table entries: 8192 (order: 3, 32768 bytes)

[ 0.000000] Writing ErrCtl register=00001079

[ 0.000000] Readback ErrCtl register=00001079

[ 0.000000] Memory: 123620k/131072k available (4314k kernel code, 7452k reserved, 1226k data, 212k init, 0k highmem)

[ 0.000000] Hierarchical RCU implementation.

[ 0.000000] NR_IRQS:128

[ 0.000000] console [ttyS1] enabled

[ 0.116000] Calibrating delay loop... 574.46 BogoMIPS (lpj=1148928)

[ 0.148000] pid_max: default: 32768 minimum: 301

[ 0.152000] Mount-cache hash table entries: 512

[ 0.156000] launch: starting cpu1

[ 0.160000] launch: cpu1 gone!

[ 0.160000] Primary instruction cache 32kB, 4-way, VIPT, linesize 32 bytes.

[ 0.160000] Primary data cache 32kB, 4-way, PIPT, no aliases, linesize 32 bytes

[ 0.160000] MIPS secondary cache 256kB, 8-way, linesize 32 bytes.

[ 0.160000] CPU1 revision is: 0001992f (MIPS 1004Kc)

[ 0.192000] Synchronize counters for CPU 1: done.

[ 0.196000] launch: starting cpu2

[ 0.200000] launch: cpu2 gone!

[ 0.200000] Primary instruction cache 32kB, 4-way, VIPT, linesize 32 bytes.

[ 0.200000] Primary data cache 32kB, 4-way, PIPT, no aliases, linesize 32 bytes

[ 0.200000] MIPS secondary cache 256kB, 8-way, linesize 32 bytes.

[ 0.200000] CPU2 revision is: 0001992f (MIPS 1004Kc)

[ 0.232000] Synchronize counters for CPU 2: done.

[ 0.236000] launch: starting cpu3

[ 0.240000] launch: cpu3 gone!

[ 0.240000] Primary instruction cache 32kB, 4-way, VIPT, linesize 32 bytes.

[ 0.240000] Primary data cache 32kB, 4-way, PIPT, no aliases, linesize 32 bytes

[ 0.240000] MIPS secondary cache 256kB, 8-way, linesize 32 bytes.

[ 0.240000] CPU3 revision is: 0001992f (MIPS 1004Kc)

[ 0.268000] Synchronize counters for CPU 3: done.

[ 0.272000] Brought up 4 CPUs

[ 0.276000] devtmpfs: initialized

[ 0.280000] NET: Registered protocol family 16

[ 0.576000] release PCIe RST: RALINK_RSTCTRL = 7000000

[ 0.580000] PCIE PHY initialize

[ 0.584000] ***** Xtal 40MHz *****

[ 0.588000] start MT7621 PCIe register access

[ 1.180000] RALINK_RSTCTRL = 7000000

[ 1.184000] RALINK_CLKCFG1 = 77ffeff8

[ 1.188000]

[ 1.188000] *************** MT7621 PCIe RC mode *************

[ 1.680000] PCIE0 no card, disable it(RST&CLK)

[ 1.684000] PCIE1 no card, disable it(RST&CLK)

[ 1.688000] PCIE2 no card, disable it(RST&CLK)

[ 1.692000] pcie_link status = 0x0

[ 1.696000] RALINK_RSTCTRL= 0

[ 1.708000] bio: create slab <bio-0> at 0

[ 1.712000] vgaarb: loaded

[ 1.716000] SCSI subsystem initialized

[ 1.720000] usbcore: registered new interface driver usbfs

[ 1.724000] usbcore: registered new interface driver hub

[ 1.728000] usbcore: registered new device driver usb

[ 1.732000] Switching to clocksource Ralink Systick timer

[ 1.736000] NET: Registered protocol family 2

[ 1.740000] Clockevents: could not switch to one-shot mode:

[ 1.740000] MIPS is not functional.

[ 1.740000] Clockevents: could not switch to one-shot mode:

[ 1.740000] MIPS is not functional.

[ 1.740000] Could not switch to high resolution mode on CPU 1

[ 1.740000] Clockevents: could not switch to one-shot mode: MIPS is not functional.

[ 1.740000] Could not switch to high resolution mode on CPU 0

[ 1.740000] Could not switch to high resolution mode on CPU 3

[ 1.828000] Clockevents: could not switch to one-shot mode: MIPS is not functional.

[ 1.844000] Could not switch to high resolution mode on CPU 2

[ 1.856000] TCP established hash table entries: 1024 (order: 1, 8192 bytes)

[ 1.872000] TCP bind hash table entries: 1024 (order: 1, 8192 bytes)

[ 1.884000] TCP: Hash tables configured (established 1024 bind 1024)

[ 1.896000] TCP: reno registered

[ 1.904000] UDP hash table entries: 256 (order: 1, 8192 bytes)

[ 1.916000] UDP-Lite hash table entries: 256 (order: 1, 8192 bytes)

[ 1.928000] NET: Registered protocol family 1

[ 1.940000] squashfs: version 4.0 (2009/01/31) Phillip Lougher

[ 1.952000] jffs2: version 2.2. (NAND) (SUMMARY) (LZMA) (RTIME) (CMODE_PRIORITY) (c) 2001-2006 Red Hat, Inc.

[ 1.972000] fuse init (API version 7.22)

[ 1.980000] msgmni has been set to 241

[ 1.988000] io scheduler noop registered (default)

[ 1.996000] reg_int_mask=0, INT_MASK= 0

[ 2.004000] HSDMA_init

[ 2.008000]

[ 2.008000] hsdma_phy_tx_ring0 = 0x00c00000, hsdma_tx_ring0 = 0xa0c00000

[ 2.028000]

[ 2.028000] hsdma_phy_rx_ring0 = 0x00c04000, hsdma_rx_ring0 = 0xa0c04000

[ 2.044000] TX_CTX_IDX0 = 0

[ 2.048000] TX_DTX_IDX0 = 0

[ 2.052000] RX_CRX_IDX0 = 3ff

[ 2.060000] RX_DRX_IDX0 = 0

[ 2.064000] set_fe_HSDMA_glo_cfg

[ 2.072000] HSDMA_GLO_CFG = 465

[ 2.080000] Serial: 8250/16550 driver, 2 ports, IRQ sharing disabled

[ 2.092000] serial8250: ttyS0 at MMIO 0x1e000d00 (irq = 27) is a 16550A

[ 2.108000] serial8250: ttyS1 at MMIO 0x1e000c00 (irq = 26) is a 16550A

[ 2.120000] Ralink gpio driver initialized

[ 2.128000] Enable Ralink GDMA Controller Module

[ 2.136000] GDMA IP Version=3

[ 2.144000] spidrv_major = 217

[ 2.148000] MediaTek Nand driver init, version v2.1 Fix AHB virt2phys error

[ 2.164000] Allocate 16 byte aligned buffer: 815ee1d0

[ 2.172000] Enable NFI Clock

[ 2.180000] # MTK NAND # : Use HW ECC

[ 2.188000] NAND ID [C8 D1 80 95 40, 00809540]

[ 2.196000] Device found in MTK table, ID: c8d1, EXT_ID: 809540

[ 2.208000] Support this Device in MTK table! c8d1

[ 2.216000] NAND device: Manufacturer ID: 0xc8, Chip ID: 0xd1 (Unknown NAND 128MiB 3,3V 8-bit), 128MiB, page size: 2048, OOB size: 64

[ 2.240000] [NAND]select ecc bit:4, sparesize :64 spare_per_sector=16

[ 2.252000] Scanning device for bad blocks

[ 2.404000] Signature matched and data read!

[ 2.412000] load_fact_bbt success 1023

[ 2.420000] 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

[ 2.440000] 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

[ 2.460000] 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

[ 2.480000] 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

[ 2.500000] 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

[ 2.520000] 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

[ 2.540000] 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

[ 2.560000] 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00 00

[ 2.580000] Creating 6 MTD partitions on "MT7621-NAND":

[ 2.588000] 0x000000000000-0x000007f80000 : "ALL"

[ 2.632000] 0x000000000000-0x000000080000 : "Bootloader"

[ 2.644000] 0x000000080000-0x0000000a0000 : "Config"

[ 2.656000] 0x0000000a0000-0x0000000c0000 : "Factory"

[ 2.664000] 0x000000140000-0x000007f80000 : "firmware"

[ 2.712000] 0x000000340000-0x000007f80000 : "rootfs"

[ 2.756000] PART->MTD.SIZE : 130285568 270658437120 3407872

[ 2.768000] mtd: partition "rootfs_data" created automatically, ofs=0x4800000, len=0x3780000

[ 2.784000] 0x000004800000-0x000007f80000 : "rootfs_data"

[ 2.808000] 0x0000024a0000-0x000004800000 : "firmware2"

[ 2.832000] [mtk_nand] probe successfully!

[ 2.840000] rootfs = 340000 to 4800000

[ 2.844000] PPP generic driver version 2.4.2

[ 2.856000] PPP BSD Compression module registered

[ 2.864000] PPP Deflate Compression module registered

[ 2.872000] PPP MPPE Compression module registered

[ 2.884000] NET: Registered protocol family 24

[ 2.892000] PPTP driver version 0.8.5

[ 2.900000] rdm_major = 253

[ 2.908000] GMAC1_MAC_ADRH -- : 0x0000000c

[ 2.916000] GMAC1_MAC_ADRL -- : 0x43288007

[ 2.924000] Ralink APSoC Ethernet Driver Initilization. v3.1 1024 rx/tx descriptors allocated, mtu = 1500!

[ 2.940000] GMAC1_MAC_ADRH -- : 0x0000000c

[ 2.948000] GMAC1_MAC_ADRL -- : 0x43288013

[ 2.960000] PROC INIT OK!

[ 2.964000] usbcore: registered new interface driver cdc_ether

[ 2.976000] usbcore: registered new interface driver cdc_eem

[ 2.988000] usbcore: registered new interface driver rndis_host

[ 3.000000] usbcore: registered new interface driver cdc_subset

[ 3.012000] usbcore: registered new interface driver usblp

[ 3.020000] usbcore: registered new interface driver usb-storage

[ 3.032000] Netfilter messages via NETLINK v0.30.

[ 3.044000] nf_conntrack version 0.5.0 (1931 buckets, 7724 max)

[ 3.056000] ipip: IPv4 over IPv4 tunneling driver

[ 3.064000] gre: GRE over IPv4 demultiplexor driver

[ 3.076000] ip_tables: (C) 2000-2006 Netfilter Core Team

[ 3.084000] Type=Linux

[ 3.092000] TCP: cubic registered

[ 3.096000] Twin IP Module Init

[ 3.104000] --> Init Smart QoS Monitor

[ 3.112000] Initializing XFRM netlink socket

[ 3.120000] NET: Registered protocol family 17

[ 3.128000] NET: Registered protocol family 15

[ 3.136000] Ebtables v2.0 registered

[ 3.144000] l2tp_core: L2TP core driver, V2.0

[ 3.152000] l2tp_ppp: PPPoL2TP kernel driver, V2.0

[ 3.164000] 8021q: 802.1Q VLAN Support v1.8

[ 3.176000] VFS: Mounted root (squashfs filesystem) readonly on device 31:5.

[ 3.196000] devtmpfs: mounted

[ 3.204000] Freeing unused kernel memory: 212K

---> Mount devtmpfs [ Failed ]

Checking Uboot Env ---> [ OK : t5008 ]

Checking System Requirements *******************************************

DRAM SIZE : Requirement->128 Mbytes / Mounted->128 Mbytes -----------> [OK]

FLASH SIZE : Requirement->128 Mbytes / Mounted->256 Mbytes -----------> [OK] Bigger Flash memory is used.

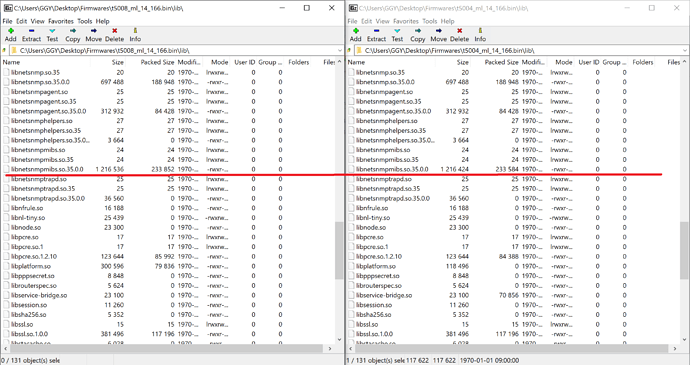

now the problem is I do not have t5004 at hand to compare any of the internal logs to see if they have any internal differences....

also it seems it has access to 256mb of flash? which i think differs from thier spec sheet which is wierd