Well fk them i just found a way to fix it and fix any regression from this change...

Ready for the big hack?

But first some explanation. Problem here is that 100% maintainers will complain about this change.

Again merging the changes to the driver will result in a kernel panic as the DTS still has the old values (and maintainers explained that DTS and arm code are merged separately so we can have a small window where the platform is completely broken.)

I had the same exact problem when i converted the entire gcc driver to parent_data and they said that I had to keep the fixed clock definition in the gcc driver even if they are declared in DTS as fixed clock.

Same happens here but even worse. The main problem here is that the driver use parent_names while what i'm doing here is converting it to parent_data using the fw_name definition. Fw_name checks if the dev have the clk defined and try to use them. And here comes the problem.

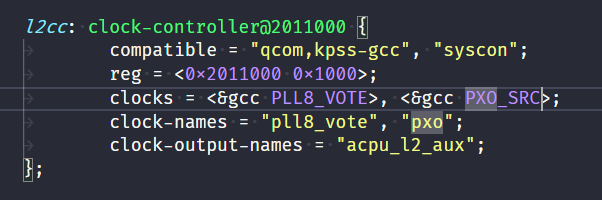

While acpu0/1_aux clk doesn't have any clock definition (cause fk Documentation pushed in the same series) the l2_aux clk have clk defined. And the pxo clk is defined using the stupid <gcc PXO_SRC>

Now PXO_SRC exist in the include but is not present in the clk table.

This little thing cause the kernel to panic as the clk when it does try to find the parent, find the defined pxo clk defined in the DTS, try to fetch it from the gcc driver and found that is not defined and the kernel panics.

Problem is that we can't change DTS, or we can but we still have to give a way to make the driver work with the old implementation.

And here the big hack at the start...

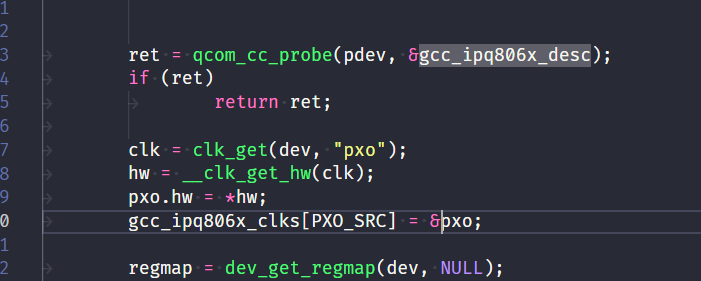

We provide a NULL pxo clk so gcc probe doesn't panic with strange values and after the probe we enter the pxo clk manually. This way when PXO_SRC is searched in the gcc clk table is found and the kernel doesn't crash

This is so wrong but still i think it's the only way to permit the conversion...

FUN THING.

Also interesting thing how the mux state is leaved... the secondary mux is set in a strange state...

cpu0 set to pll8 (384mhz) l2 and cpu1 to pxo (25mhz) While this doesn't make any difference as we always source out of qsb it's still strange...

Anyway don't know why but with these change i have these values from mbw. 900mib/s and 190mib/s are a record I assume...

root@OpenWrt:/# ./mbw 32

Long uses 4 bytes. Allocating 2*8388608 elements = 67108864 bytes of memory.

Using 262144 bytes as blocks for memcpy block copy test.

Getting down to business... Doing 10 runs per test.

0 Method: MEMCPY Elapsed: 0.03592 MiB: 32.00000 Copy: 890.918 MiB/s

1 Method: MEMCPY Elapsed: 0.03582 MiB: 32.00000 Copy: 893.306 MiB/s

2 Method: MEMCPY Elapsed: 0.03576 MiB: 32.00000 Copy: 894.755 MiB/s

3 Method: MEMCPY Elapsed: 0.03586 MiB: 32.00000 Copy: 892.409 MiB/s

4 Method: MEMCPY Elapsed: 0.03562 MiB: 32.00000 Copy: 898.246 MiB/s

5 Method: MEMCPY Elapsed: 0.03562 MiB: 32.00000 Copy: 898.271 MiB/s

6 Method: MEMCPY Elapsed: 0.03578 MiB: 32.00000 Copy: 894.454 MiB/s

7 Method: MEMCPY Elapsed: 0.03559 MiB: 32.00000 Copy: 899.230 MiB/s

8 Method: MEMCPY Elapsed: 0.03563 MiB: 32.00000 Copy: 898.094 MiB/s

9 Method: MEMCPY Elapsed: 0.03667 MiB: 32.00000 Copy: 872.648 MiB/s

AVG Method: MEMCPY Elapsed: 0.03583 MiB: 32.00000 Copy: 893.171 MiB/s

0 Method: DUMB Elapsed: 0.17263 MiB: 32.00000 Copy: 185.364 MiB/s

1 Method: DUMB Elapsed: 0.17124 MiB: 32.00000 Copy: 186.874 MiB/s

2 Method: DUMB Elapsed: 0.17121 MiB: 32.00000 Copy: 186.906 MiB/s

3 Method: DUMB Elapsed: 0.17123 MiB: 32.00000 Copy: 186.878 MiB/s

4 Method: DUMB Elapsed: 0.17134 MiB: 32.00000 Copy: 186.768 MiB/s

5 Method: DUMB Elapsed: 0.17170 MiB: 32.00000 Copy: 186.369 MiB/s

6 Method: DUMB Elapsed: 0.17261 MiB: 32.00000 Copy: 185.391 MiB/s

7 Method: DUMB Elapsed: 0.17114 MiB: 32.00000 Copy: 186.980 MiB/s

8 Method: DUMB Elapsed: 0.17120 MiB: 32.00000 Copy: 186.916 MiB/s

9 Method: DUMB Elapsed: 0.17119 MiB: 32.00000 Copy: 186.924 MiB/s

AVG Method: DUMB Elapsed: 0.17155 MiB: 32.00000 Copy: 186.535 MiB/s

0 Method: MCBLOCK Elapsed: 0.03591 MiB: 32.00000 Copy: 891.141 MiB/s

1 Method: MCBLOCK Elapsed: 0.03593 MiB: 32.00000 Copy: 890.720 MiB/s

2 Method: MCBLOCK Elapsed: 0.03604 MiB: 32.00000 Copy: 888.001 MiB/s

3 Method: MCBLOCK Elapsed: 0.03597 MiB: 32.00000 Copy: 889.680 MiB/s

4 Method: MCBLOCK Elapsed: 0.03585 MiB: 32.00000 Copy: 892.683 MiB/s

5 Method: MCBLOCK Elapsed: 0.03589 MiB: 32.00000 Copy: 891.688 MiB/s

6 Method: MCBLOCK Elapsed: 0.03691 MiB: 32.00000 Copy: 866.997 MiB/s

7 Method: MCBLOCK Elapsed: 0.03574 MiB: 32.00000 Copy: 895.355 MiB/s

8 Method: MCBLOCK Elapsed: 0.03810 MiB: 32.00000 Copy: 839.829 MiB/s

9 Method: MCBLOCK Elapsed: 0.03589 MiB: 32.00000 Copy: 891.737 MiB/s

AVG Method: MCBLOCK Elapsed: 0.03622 MiB: 32.00000 Copy: 883.465 MiB/s

Wait wth? reverting qsb to a rate of 1 (aka make the sec mux sourcing out of pll8_vote i have these results??)

root@OpenWrt:/# ./mbw 32

Long uses 4 bytes. Allocating 2*8388608 elements = 67108864 bytes of memory.

Using 262144 bytes as blocks for memcpy block copy test.

Getting down to business... Doing 10 runs per test.

0 Method: MEMCPY Elapsed: 0.04374 MiB: 32.00000 Copy: 731.596 MiB/s

1 Method: MEMCPY Elapsed: 0.04379 MiB: 32.00000 Copy: 730.827 MiB/s

2 Method: MEMCPY Elapsed: 0.04359 MiB: 32.00000 Copy: 734.130 MiB/s

3 Method: MEMCPY Elapsed: 0.04368 MiB: 32.00000 Copy: 732.601 MiB/s

4 Method: MEMCPY Elapsed: 0.04389 MiB: 32.00000 Copy: 729.079 MiB/s

5 Method: MEMCPY Elapsed: 0.04573 MiB: 32.00000 Copy: 699.698 MiB/s

6 Method: MEMCPY Elapsed: 0.04379 MiB: 32.00000 Copy: 730.827 MiB/s

7 Method: MEMCPY Elapsed: 0.04775 MiB: 32.00000 Copy: 670.199 MiB/s

8 Method: MEMCPY Elapsed: 0.04370 MiB: 32.00000 Copy: 732.332 MiB/s

9 Method: MEMCPY Elapsed: 0.04637 MiB: 32.00000 Copy: 690.072 MiB/s

AVG Method: MEMCPY Elapsed: 0.04460 MiB: 32.00000 Copy: 717.455 MiB/s

0 Method: DUMB Elapsed: 0.17335 MiB: 32.00000 Copy: 184.597 MiB/s

1 Method: DUMB Elapsed: 0.17300 MiB: 32.00000 Copy: 184.969 MiB/s

2 Method: DUMB Elapsed: 0.17345 MiB: 32.00000 Copy: 184.494 MiB/s

3 Method: DUMB Elapsed: 0.17314 MiB: 32.00000 Copy: 184.816 MiB/s

4 Method: DUMB Elapsed: 0.17484 MiB: 32.00000 Copy: 183.020 MiB/s

5 Method: DUMB Elapsed: 0.17862 MiB: 32.00000 Copy: 179.154 MiB/s

6 Method: DUMB Elapsed: 0.17318 MiB: 32.00000 Copy: 184.777 MiB/s

7 Method: DUMB Elapsed: 0.17310 MiB: 32.00000 Copy: 184.866 MiB/s

8 Method: DUMB Elapsed: 0.17301 MiB: 32.00000 Copy: 184.960 MiB/s

9 Method: DUMB Elapsed: 0.17298 MiB: 32.00000 Copy: 184.988 MiB/s

AVG Method: DUMB Elapsed: 0.17387 MiB: 32.00000 Copy: 184.048 MiB/s

0 Method: MCBLOCK Elapsed: 0.04373 MiB: 32.00000 Copy: 731.713 MiB/s

1 Method: MCBLOCK Elapsed: 0.04411 MiB: 32.00000 Copy: 725.476 MiB/s

2 Method: MCBLOCK Elapsed: 0.04579 MiB: 32.00000 Copy: 698.797 MiB/s

3 Method: MCBLOCK Elapsed: 0.04390 MiB: 32.00000 Copy: 728.846 MiB/s

4 Method: MCBLOCK Elapsed: 0.04786 MiB: 32.00000 Copy: 668.589 MiB/s

5 Method: MCBLOCK Elapsed: 0.04388 MiB: 32.00000 Copy: 729.262 MiB/s

6 Method: MCBLOCK Elapsed: 0.04683 MiB: 32.00000 Copy: 683.337 MiB/s

7 Method: MCBLOCK Elapsed: 0.04389 MiB: 32.00000 Copy: 729.112 MiB/s

8 Method: MCBLOCK Elapsed: 0.04376 MiB: 32.00000 Copy: 731.211 MiB/s

9 Method: MCBLOCK Elapsed: 0.04386 MiB: 32.00000 Copy: 729.528 MiB/s

AVG Method: MCBLOCK Elapsed: 0.04476 MiB: 32.00000 Copy: 714.881 MiB/s