I have, for one of my 3 E8450s. I think I went from v0.x to v1.0.2 installer, all the while running my own master builds. Have not encountered OKD myself as well.

My steps are as follows:

Stock firmware → Owrt v1.0.3 → OpenWRT 23.05.2 → Update bl2+uboot.fip using u-boot TFTP → sysupgrade to OpenWRT 23.05.3 .

So upgrading bootloader doesn't actually help, does it?

It will be helpful once the bootloader has been properly updated with the full driving strength and when the write operation takes place with the full driving strength already applied. However, the bootloader hasn't yet received the necessary patches. That means that when you did the TFTP update, you updated the bootloader using the reduced driving strength and therefore theoretically put the device at risk of experiencing the issue.

Is there a way to check if the driving strength is correct?

My understanding is that the driving strength value is stored in the bootloader, could I set the driving strength manually?

(edited for clarity and correctness)

Although you can read the value via Linux, we still can't set the proper strength on the bootloader until the code is officially updated. Since it's a signed binary, altering it the hard way would invalidate the "trusted" signature and so it would refuse to load.

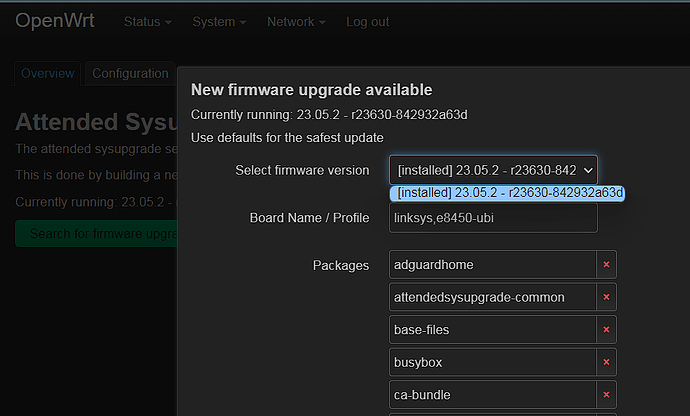

I've scoured the thread and I think i have it correct that I need to do a full 'install script' to update the UBI layout. To avoid bricking my device when upgrading to 23.05.3 (or later) I'm looking for clarity just to be safe ![]()

I have:

Linksys E8450 (UBI)

OpenWrt 23.05.2 r23630-842932a63d / LuCI openwrt-23.05 branch git-24.067.02086-146a8f1

This was converted from stock in October 2022.

Do I need to go through the full installation process from: GitHub - dangowrt/owrt-ubi-installer: OpenWrt firmware installer for the Linksys E8450 aka. Belkin RT3200

Thanks for the clarity!

If you're on 23.05.2, you just need to do Attended Sysupgrade to go to 23.05.3 and keep your settings. That's it.

When OpenWRT v24 arrives, or if you want to run a Snapshot build, then you need to run the updated Installer from the github page. But it's better to stay in Stable for now, until clear instructions are added to the Wiki.

Cheers!

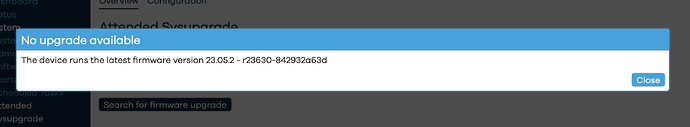

I checked my Linksys E8450 (UBI) with OpenWrt 23.05.2 r23630-842932a63d / LuCI openwrt-23.05 branch git-23.306.39416-c86c256, there is no

version 25.05.3

That's weird. I've updated my RT3200 yesterday just like that.

There's must be something on the sysupgrade server that's not allowing to offer 23.05.3. On my device actually offers me 23.05.2:

Maybe, they're pulling out 23.05.3 to a unspecified bug.

In any case, just wait for at least today to see what happened.

cat /sys/kernel/debug/pinctrl/*/pinconf-pins

... which came already yesterday:

Mailing list

The attended-sysupgrade servers take a bit more time (and used to take more work, too) when a new release comes out. They likely haven't updated the code and/or caches yet. It's still accessible under the firmware selector/builder, however.

These are my values:

root@rt3200:~# cat /sys/kernel/debug/pinctrl/*/pinconf-pins

Pin config settings per pin

Format: pin (name): configs

pin 0 (GPIO_A): input bias disabled, output drive strength (8 mA), input enabled, input schmitt enabled, slew rate (1), tdsel (10), rdsel (12)

pin 1 (I2S1_IN): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 2 (I2S1_OUT): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 3 (I2S_BCLK): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 4 (I2S_WS): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 5 (I2S_MCLK): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 6 (TXD0): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 7 (RXD0): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 8 (SPI_WP): input bias disabled, output drive strength (12 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 9 (SPI_HOLD): input bias disabled, output drive strength (12 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 10 (SPI_CLK): input bias disabled, output drive strength (12 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 11 (SPI_MOSI): input bias disabled, output drive strength (12 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 12 (SPI_MISO): input bias disabled, output drive strength (12 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 13 (SPI_CS): input bias pull up (1 ohms), output drive strength (12 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 14 (I2C_SDA): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 15 (I2C_SCL): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 16 (I2S2_IN): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 17 (I2S3_IN): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 18 (I2S4_IN): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 19 (I2S2_OUT): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 20 (I2S3_OUT): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 21 (I2S4_OUT): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 22 (GPIO_B): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 23 (MDC): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 24 (MDIO): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 25 (G2_TXD0): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 26 (G2_TXD1): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 27 (G2_TXD2): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 28 (G2_TXD3): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 29 (G2_TXEN): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 30 (G2_TXC): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 31 (G2_RXD0): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 32 (G2_RXD1): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 33 (G2_RXD2): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 34 (G2_RXD3): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 35 (G2_RXDV): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 36 (G2_RXC): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 37 (NCEB): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 38 (NWEB): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 39 (NREB): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 40 (NDL4): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 41 (NDL5): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 42 (NDL6): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 43 (NDL7): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 44 (NRB): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 45 (NCLE): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 46 (NALE): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 47 (NDL0): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 48 (NDL1): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 49 (NDL2): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 50 (NDL3): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 51 (MDI_TP_P0): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 52 (MDI_TN_P0): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 53 (MDI_RP_P0): input bias disabled, output drive strength (8 mA), input enabled, input schmitt enabled, tdsel (10), rdsel (12)

pin 54 (MDI_RN_P0): input bias disabled, output drive strength (8 mA), output enabled, tdsel (10), rdsel (12)

pin 55 (MDI_TP_P1): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 56 (MDI_TN_P1): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 57 (MDI_RP_P1): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 58 (MDI_RN_P1): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 59 (MDI_RP_P2): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 60 (MDI_RN_P2): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 61 (MDI_TP_P2): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 62 (MDI_TN_P2): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 63 (MDI_TP_P3): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 64 (MDI_TN_P3): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 65 (MDI_RP_P3): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 66 (MDI_RN_P3): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 67 (MDI_RP_P4): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 68 (MDI_RN_P4): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 69 (MDI_TP_P4): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 70 (MDI_TN_P4): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 71 (PMIC_SCL): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 72 (PMIC_SDA): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 73 (SPIC1_CLK): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 74 (SPIC1_MOSI): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 75 (SPIC1_MISO): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 76 (SPIC1_CS): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 77 (GPIO_D): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 78 (WATCHDOG): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 79 (RTS3_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 80 (CTS3_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 81 (TXD3): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 82 (RXD3): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 83 (PERST0_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 84 (PERST1_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 85 (WLED_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 86 (EPHY_LED0_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 87 (AUXIN0): input bias disabled, output drive strength (4 mA), input enabled, tdsel (0), rdsel (12)

pin 88 (AUXIN1): input bias disabled, output drive strength (4 mA), input enabled, tdsel (0), rdsel (12)

pin 89 (AUXIN2): input bias disabled, output drive strength (4 mA), input enabled, tdsel (0), rdsel (12)

pin 90 (AUXIN3): input bias disabled, output drive strength (4 mA), input enabled, tdsel (0), rdsel (12)

pin 91 (TXD4): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 92 (RXD4): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 93 (RTS4_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 94 (CTS4_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 95 (PWM1): input bias disabled, output drive strength (8 mA), output enabled, slew rate (1), tdsel (10), rdsel (12)

pin 96 (PWM2): input bias disabled, output drive strength (8 mA), output enabled, slew rate (1), tdsel (10), rdsel (12)

pin 97 (PWM3): input bias disabled, output drive strength (8 mA), output enabled, slew rate (1), tdsel (10), rdsel (12)

pin 98 (PWM4): input bias disabled, output drive strength (8 mA), output enabled, slew rate (1), tdsel (10), rdsel (12)

pin 99 (PWM5): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 100 (PWM6): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 101 (PWM7): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 102 (GPIO_E): input bias disabled, output drive strength (8 mA), input enabled, input schmitt enabled, slew rate (1), tdsel (10), rdsel (12)

I am one of the ones who has to use the "refrigerator trick" to get my RT3200 to boot these days, on v1.1.1

Upgraded to 23.05.3 and only these warning/errors in the logread

Fri Mar 22 23:09:43 2024 [1711145383.961] kern.warn kernel: [ 0.050227] CPU features: SANITY CHECK: Unexpected variation in SYS_CNTFRQ_EL0. Boot CPU: 0x00000000bebc20, CPU1: 0x00000000000000

Fri Mar 22 23:09:43 2024 [1711145383.961] kern.warn kernel: [ 0.050247] CPU features: Unsupported CPU feature variation detected.

Fri Mar 22 23:09:43 2024 [1711145383.962] kern.err kernel: [ 0.401771] mt7622-pinctrl 10211000.pinctrl: invalid group "pwm_ch7_2" for function "pwm"

Fri Mar 22 23:09:43 2024 [1711145383.962] kern.err kernel: [ 0.414524] mt-pmic-pwrap 10001000.pwrap: unexpected interrupt int=0x1

Fri Mar 22 23:09:43 2024 [1711145383.962] kern.warn kernel: [ 0.543821] hwrng: no data available

Fri Mar 22 23:09:43 2024 [1711145383.962] kern.err kernel: [ 0.600458] OF: Bad cell count for /spi@1100d000/flash@0/partitions

Fri Mar 22 23:09:43 2024 [1711145383.962] kern.err kernel: [ 0.606775] OF: Bad cell count for /spi@1100d000/flash@0/partitions

Fri Mar 22 23:09:43 2024 [1711145383.962] kern.err kernel: [ 0.920604] mtk-wdt 10212000.watchdog: IRQ index 0 not found

Fri Mar 22 23:09:43 2024 [1711145383.966] kern.warn kernel: [ 5.761409] overlayfs: null uuid detected in lower fs '/', falling back to xino=off,index=off,nfs_export=off.

Fri Mar 22 23:09:44 2024 [1711145384.572] daemon.warn dnsmasq[1]: no servers found in /tmp/resolv.conf.d/resolv.conf.auto, will retry

Fri Mar 22 23:09:45 2024 [1711145385.539] daemon.notice procd: /etc/rc.d/S25packet_steering: sh: write error: No such file or directory

Fri Mar 22 23:09:45 2024 [1711145385.559] daemon.notice procd: /etc/rc.d/S25packet_steering: sh: write error: No such file or directory

Fri Mar 22 23:09:46 2024 [1711145386.063] daemon.err uhttpd[1968]: bind(): Address not available

Fri Mar 22 23:09:46 2024 [1711145386.064] daemon.err uhttpd[1968]: bind(): Address not available

Fri Mar 22 23:09:46 2024 [1711145386.064] daemon.err uhttpd[1968]: Error: No sockets bound, unable to continue

Fri Mar 22 23:09:46 2024 [1711145386.148] daemon.warn netifd: You have delegated IPv6-prefixes but haven't assigned them to any interface. Did you forget to set option ip6assign on your lan-interfaces?

Fri Mar 22 23:09:46 2024 [1711145386.317] daemon.notice netifd: radio1 (2066): WARNING: Variable 'data' does not exist or is not an array/object

Tue Mar 26 20:13:09 2024 [1711480389.326] cron.err crond[1902]: time disparity of 5583 minutes detected

Can presume we are safe-ish. So far so good. Used Luci to upgrade as always.

What does good look like?

This is the output on mine. I've yet to experience the OKD. Lucky I guess?

cat /sys/kernel/debug/pinctrl/*/pinconf-pins

Pin config settings per pin

Format: pin (name): configs

pin 0 (GPIO_A): input bias disabled, output drive strength (8 mA), input enabled, input schmitt enabled, slew rate (1), tdsel (10), rdsel (12)

pin 1 (I2S1_IN): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 2 (I2S1_OUT): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 3 (I2S_BCLK): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 4 (I2S_WS): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 5 (I2S_MCLK): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 6 (TXD0): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 7 (RXD0): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 8 (SPI_WP): input bias disabled, output drive strength (12 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 9 (SPI_HOLD): input bias disabled, output drive strength (12 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 10 (SPI_CLK): input bias disabled, output drive strength (12 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 11 (SPI_MOSI): input bias disabled, output drive strength (12 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 12 (SPI_MISO): input bias disabled, output drive strength (12 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 13 (SPI_CS): input bias pull up (1 ohms), output drive strength (12 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 14 (I2C_SDA): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 15 (I2C_SCL): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 16 (I2S2_IN): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 17 (I2S3_IN): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 18 (I2S4_IN): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 19 (I2S2_OUT): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 20 (I2S3_OUT): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 21 (I2S4_OUT): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 22 (GPIO_B): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 23 (MDC): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 24 (MDIO): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 25 (G2_TXD0): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 26 (G2_TXD1): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 27 (G2_TXD2): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 28 (G2_TXD3): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 29 (G2_TXEN): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 30 (G2_TXC): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 31 (G2_RXD0): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 32 (G2_RXD1): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 33 (G2_RXD2): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 34 (G2_RXD3): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 35 (G2_RXDV): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 36 (G2_RXC): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 37 (NCEB): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 38 (NWEB): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 39 (NREB): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 40 (NDL4): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 41 (NDL5): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 42 (NDL6): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 43 (NDL7): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 44 (NRB): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 45 (NCLE): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 46 (NALE): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 47 (NDL0): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 48 (NDL1): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 49 (NDL2): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 50 (NDL3): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (0), rdsel (12)

pin 51 (MDI_TP_P0): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 52 (MDI_TN_P0): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 53 (MDI_RP_P0): input bias disabled, output drive strength (8 mA), input enabled, input schmitt enabled, tdsel (10), rdsel (12)

pin 54 (MDI_RN_P0): input bias disabled, output drive strength (8 mA), output enabled, tdsel (10), rdsel (12)

pin 55 (MDI_TP_P1): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 56 (MDI_TN_P1): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 57 (MDI_RP_P1): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 58 (MDI_RN_P1): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 59 (MDI_RP_P2): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 60 (MDI_RN_P2): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 61 (MDI_TP_P2): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 62 (MDI_TN_P2): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 63 (MDI_TP_P3): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 64 (MDI_TN_P3): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 65 (MDI_RP_P3): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 66 (MDI_RN_P3): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 67 (MDI_RP_P4): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 68 (MDI_RN_P4): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 69 (MDI_TP_P4): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 70 (MDI_TN_P4): input bias disabled, output drive strength (8 mA), input enabled, tdsel (10), rdsel (12)

pin 71 (PMIC_SCL): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 72 (PMIC_SDA): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 73 (SPIC1_CLK): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 74 (SPIC1_MOSI): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 75 (SPIC1_MISO): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 76 (SPIC1_CS): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 77 (GPIO_D): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 78 (WATCHDOG): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 79 (RTS3_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 80 (CTS3_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 81 (TXD3): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 82 (RXD3): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 83 (PERST0_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 84 (PERST1_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 85 (WLED_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 86 (EPHY_LED0_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 87 (AUXIN0): input bias disabled, output drive strength (4 mA), input enabled, tdsel (0), rdsel (12)

pin 88 (AUXIN1): input bias disabled, output drive strength (4 mA), input enabled, tdsel (0), rdsel (12)

pin 89 (AUXIN2): input bias disabled, output drive strength (4 mA), input enabled, tdsel (0), rdsel (12)

pin 90 (AUXIN3): input bias disabled, output drive strength (4 mA), input enabled, tdsel (0), rdsel (12)

pin 91 (TXD4): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 92 (RXD4): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 93 (RTS4_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 94 (CTS4_N): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 95 (PWM1): input bias disabled, output drive strength (8 mA), output enabled, slew rate (1), tdsel (10), rdsel (12)

pin 96 (PWM2): input bias disabled, output drive strength (8 mA), output enabled, slew rate (1), tdsel (10), rdsel (12)

pin 97 (PWM3): input bias disabled, output drive strength (8 mA), output enabled, slew rate (1), tdsel (10), rdsel (12)

pin 98 (PWM4): input bias disabled, output drive strength (8 mA), output enabled, slew rate (1), tdsel (10), rdsel (12)

pin 99 (PWM5): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 100 (PWM6): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 101 (PWM7): input bias disabled, output drive strength (8 mA), input enabled, slew rate (1), tdsel (10), rdsel (12)

pin 102 (GPIO_E): input bias disabled, output drive strength (8 mA), input enabled, input schmitt enabled, slew rate (1), tdsel (10), rdsel (12)

I think we might be chasing the wrong lead in terms of driving currents?

I'm not exactly sure which SPI NAND flash that the RT3200/E8450 are using, but typically I think most will use WinBond flash ICs. I took a quick look at one of WinBond's SLC NAND specification here.

It specified a typical current of 25mA and a max of 35 mA, but there's no minimum current requirement. So this tells me it is not important.

Driving current is important for writes, while during reads, it's the NAND flash that will be supplying the output, therefore have a max driving current based on how the NAND power circuitry is designed. From my IC design course many many many moons ago, current basically is not really a concern as long as the power supply/circuitry can provide enough juice.

From what I can see, it appears that flash writes are usually OK, but somehow reading it back is problematic which requires multiple tries. This is unlikely to be a problem with the flash write current. Current is always fluctuating based on load. Most IC requires constant voltage, which in this case should be 3.3V. The entire flash IC chip will have a max power requirement, and because it's constant 3.3V, that means that during max power draw, the flash chip will draw up to a max current. During idle, it's still 3.3V but current will be lowered, so current fluctuates.

So during flash write, when a data signal is sent to the flash SPI line, it's either pulled up (3.3V) or down (0V) and current will flunctuate based on flash SPI pin load. I don't think any IC can limit the current draw. If an IC tries to draw too much current than the power circuitry can provide, a brown out will occur, and it will fry the IC chip or the chip driving the flash or both.

Just brought my first bricked unit (RT3200, 23.05.0, r23497) back to life following @daniel 's instructions. It was UBI converted when I first installed OpenWRT. I am now converted to 1.1.0 and running latest SNAPSHOT (r25667-1d33ee019f).

"force-flashing openwrt-mediatek-mt7622-linksys_e8450-ubi-initramfs-recovery-installer.itb of pre-release installer 1.1.0 you can proceed and flash openwrt-mediatek-mt7622-linksys_e8450-ubi-squashfs-sysupgrade.itb from downloads.openwrt.org."

I used one PC as a tftp server/wired LAN client and another for serial operations. I used a generic aliexpress/amazon USB to serial adapter, soldered into the pins like some animal.

On the LAN client/TFTP server (at 192.186.1.254, an arch linux device), I ran the following:

./mtk_uartboot -p bl2-mt7622-1ddr-ram.bin -a -f openwrt-23.05.2-mediatek-mt7622-linksys_e8450-ubi-bl31-uboot.fip -s /dev/ttyUSB0 ; minicom -D /dev/ttyUSB0

I could then select to boot recovery from TFTP. That would get me a recovery web interface. I then flashed the recovery installer linked above.

Once that was set, I power-cycled again and was able to boot properly, but to the recovery web interface. I then flashed the ubi-squashfs-sysupgrade, without preserving any settings (unfortunately, I don't recall whether the other two boxes were checked; the ones about preserving a package list, etc).

After booting successfully, I had no luci interface. I used the serial interface to boot into recovery and flash the ubi-squashfs-sysupgrade again, but still had no interface.

I ended up connecting the WAN interface and doing a "opkg update && opkg install luci" and that got me to a working interface. I was able to enable the radios and my clients see the new AP, and all the luci pages appear to be working properly. I'm concerned that perhaps I somehow introduced some user error during the ubi-squashfs-sysupgrade process, leading to something not working properly (like firewall, etc), but at least I now have a working AP.

I had a second RT3200 that died the other night during a power outage and will probably attempt a recovery on it this week. Thanks Daniel and all the other devs for your help with this. Hopefully this RT3200 can be put back into "production" use here at home.

Please let me know if anyone needs any debug output from this router, or the one that was bricked the other night. Happy to help in any way.

I was successfully running 1.1.1.x with the snapshot and after trying to update to the latest build, it failed with the above error and tried fixing it by running the below commands

uci set system.@system[0].compat_version="2.0"

uci commit system

After this command, I rebooted my router and now it fails to boot with no lights. Tried waiting for couple of minutes and also tried with different power sockets.

Is it completely dead now?

Try rebooting again, with the power switch. The problematic routers sometimes boot, sometimes not.

(the sysupgrade compatibility setting mentioned above has no relevance regarding booting)